Cronômetro - Placa DE0

- Detalhes

- Categoria: Exemplos com FPGA

- Publicado em Sexta, 21 Outubro 2011 20:36

- Escrito por João Marcos de Aguiar

- Acessos: 5148

Cronômetro - Placa DE0®

O projeto apresenta a implementação de um cronômetro de minutos e segundos na placa DE0®, utilizando os displays de 7 degmentos para a vizualização. O cronômetro também utilizará três botões, um de pausa, um de reset e um para parar a contagem.

Esse artigo demonstra a implementação de um projeto em VHDL, o qual foi simulado com o Modelsim-Altera® utilizando a simulação por testbench.

Equipamento utilizado: Placa DE0®.

Descrição do Funcionamento

O projeto gerará um clock de 1Hz para incrementar os valores dos segundos. Quando a contagem chegar a 60, é necessário "zerar" a contagem de segundos incrementar o contador de minutos.

Para o display de 7 segmentos será necessário um decodificador para mostrar os valores na saída. O botão de pausa congelará o valor mostrado nos displays de 7 segmentos, porém a contagem continuará. O botão stop interromperá a contagem, a qual pode ser retomada pressionando novamente este botão. O botão de reset reinicia a contagem.

Descrição em VHDL

Para a implementação do projeto, precisa-se de quatro entradas e 28 saídas, destinadas aos 4 displays de 7 segmentos e uma para o ponto do display central, o qual sempre estará em nível lógico baixo, pois os displays são do tipo anodo comum. O clock interno de 1Hz é gerado por um preescaler de 50M, pois a placa DE0® possui um clock de 50MHz.

O projeto possui 4 entradas e 29 saídas, declaradas na entidade:

O primeiro bloco do código tem como função implementar a lógica do comando de parada. Quando o botão é pressionado a variável flag muda o seu valor: se estava contando para de contar; se estava parado retorna a contar. O processo principal depende da variável flag para contar ou não.

O processo principal utiliza as variáveis apresentadas abaixo, sendo os 4 bits menos significativos dos vetores destinados as unidades e os 3 bits mais significativos destinados as dezenas. A flag funciona como registrador de estado, indicando se está contando ou está parado. A variável cont funciona como preescaler.

O bloco seguinte do código é reponsavél pelo comportamento quando o botão de reset está pressionado. São atriubuido os valores iniciais das varáveis

Quando o reset não está pressionado, o programa entra na rotina principal. Primeiramente é implementado o presescaler para a incrementar os segundos. O passo seguinte é verificar o estouro de contagem, neste caso 10 nas unidades e 6 nas dezenas.

Ao final do processo, se o botão de pausa não está pressionado, atualiza-se os valores dos sinais.

No final do código é implementado um contador para os displays de 7 segmentos. O decodificador tem como entrada o valor númerico e traduz para os segmentos que precisam ser acendidos no display. Como o display é de anodo comum, os segmentos acesos são os que estão em nível lógico baixo.

Simulação

Para simular o funcionamento do código fonte é necessário gerar os pulsos de clock e emular o pressionamento dos botões utilizados no projeto. Para que a simulação ocorra mais rapidamente pode diminuir o preescaler do código fonte. Neste teste será diminuido para 20 ms.

Primeiramente declare-se o port map.

O primeiro bloco emula o clock.

O segundo bloco tem por funcionalidade emular o pressionamento dos botões.

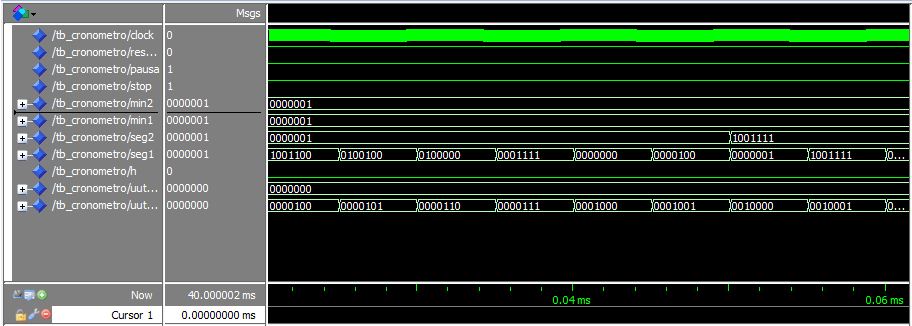

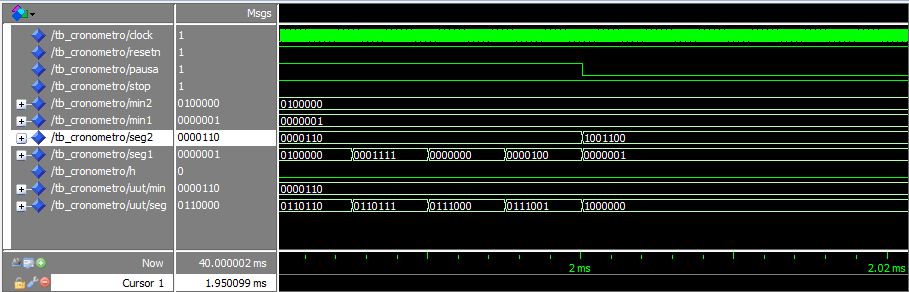

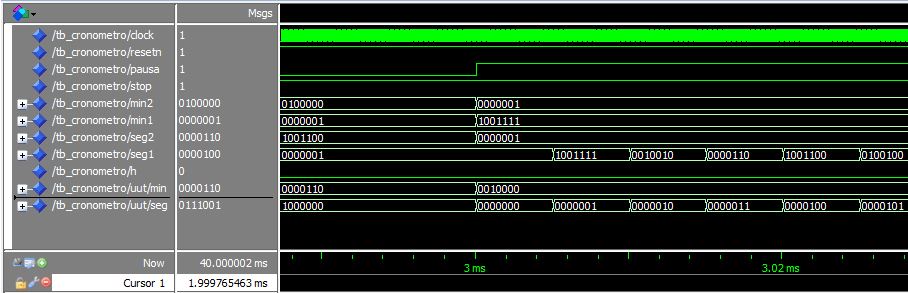

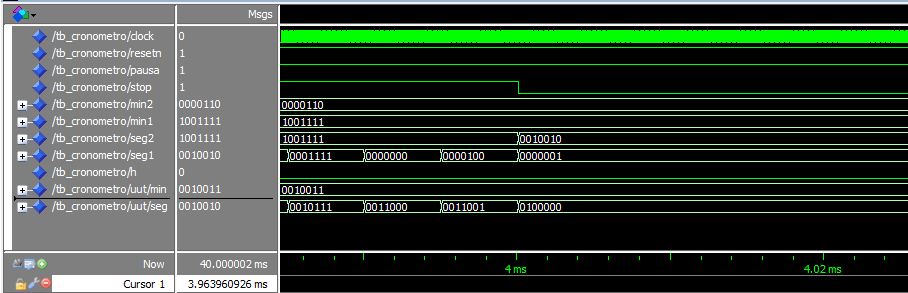

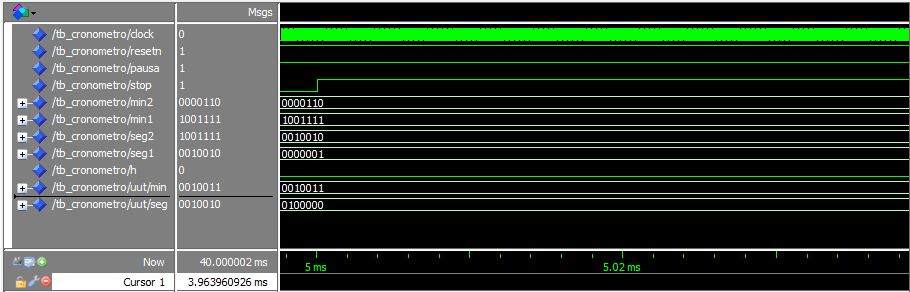

Abaixo estão apresentadas as formas de onda obtidas na simulação.

Figura 2: Instante do incrmento na dezena dos segundos.

Figura 3: Instante do pressionamento do botão de pausa.

Figura 4: Instante em que o botão de pausa é solto.

Figura 5: Instante em que é pressionado o botão de stop..

Figura 6: Instante em que o botão de stop é solto.

Figura 7: Instante em que o botão de reset é pressionado.

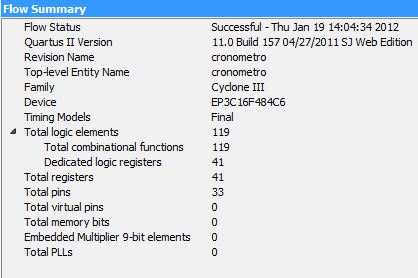

Montagem e Roteamento

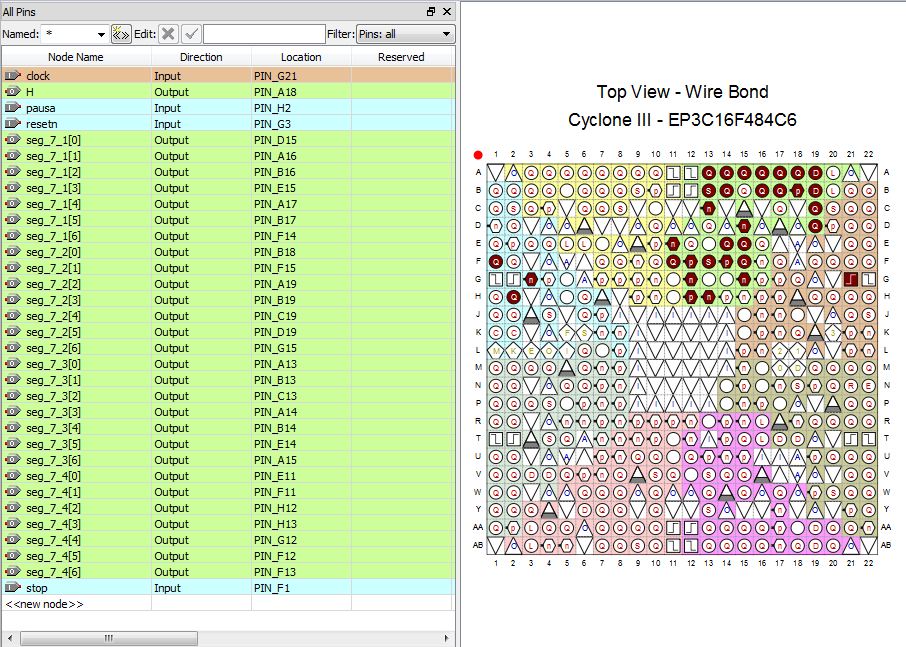

O único equipamento necessário para a implementação do projeto é a placa DE0®. Os recursos utilizados são os 4 displays de 7 segmento e os 3 push bottons. A figura abaixo apresenta a distribuição de pinos, utilizando como base o manual da placa. O FPGA presente na placa é o EP3C16F484 da família Cyclone III.

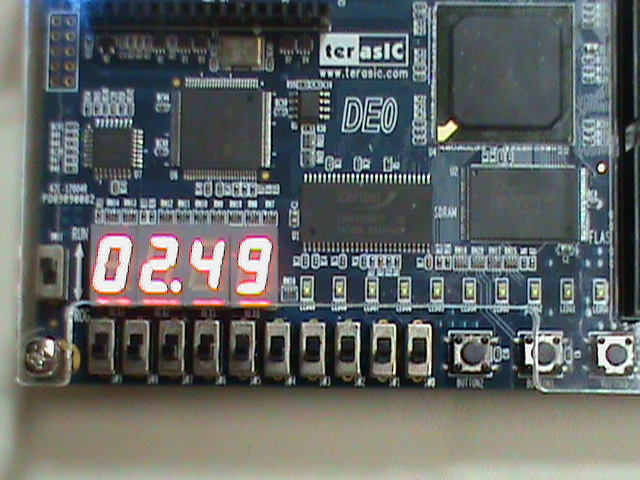

Figura 8: Cronômetro implementado na placa DE0®

Figura 9: Atribuição de pinos

Teste e Gravação

A gravação pode ser feita seguindo os procedimentos indicados no manual da placa DE0® ou seguindo o tópico de gravação no tutorial. O teste de funcionamento é mostrado no início do artigo.

Arquivos de Projeto

Links Externos

- Placa DE0 (Inglês);