Decodificador 3x8 - Modo Esquemático

- Detalhes

- Categoria: Exemplos com CPLD

- Publicado em Terça, 20 Setembro 2011 11:05

- Escrito por Marcos Vinícius Leal da Silva

- Acessos: 6795

Decodificador 3x8 - Modo Esquemático

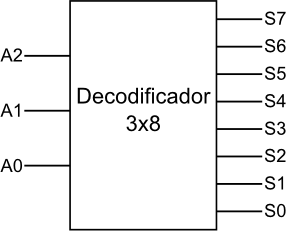

O projeto pretende a partir de um código binário de três bits, selecionar uma das oito saídas, sendo a Figura 1 o bloco representativo do mesmo. Suas aplicações vão desde multiplexadores e demultiplexadores, até seleção de memória de entrada e saída (E/S).

Figura 1: Bloco Decodificador 3x8

Este artigo será um exemplo em modo esquemático de um circuito lógico combinacional no Quartus® II, utilizando apenas componentes primitivos do mesmo. A simulação será feita pelo modo interativo no ModelSim®-Altera. No final deste exemplo há um tutorial dando noções básicas e importantes sobre "entrada em modo esquemático" no Quartus® II, além de dicas sobre "Análise e Síntese" e gravação do módulo principal.

Neste projeto será utilizado:

- 1x Módulo CPLD_7064;

- 1x Placa de Chaves;

- 1x Placa de LEDs.

Lógica de Funcionamento

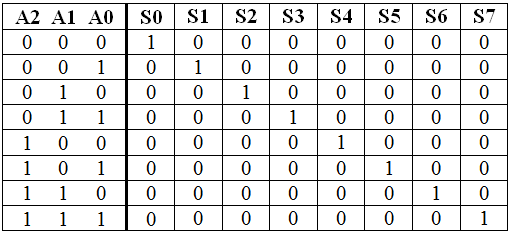

Esse projeto possui três entradas, formando um código binário de três bits (A2, A1 e A0), e oito saídas (S0 à S7). A partir do código fornecido pela entrada, o decodificador interpreta-o e seleciona uma das saídas, de acordo com a Tabela da Verdade do projeto.

Tabela 1: Tabela da Verdade do Decodificador_3x8

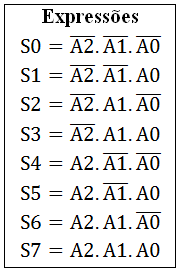

As expressões lógicas são obtidas a partir da Tabela da Verdade.

Tabela 2: Expressões Lógicas

Projeto em Modo Esquemático

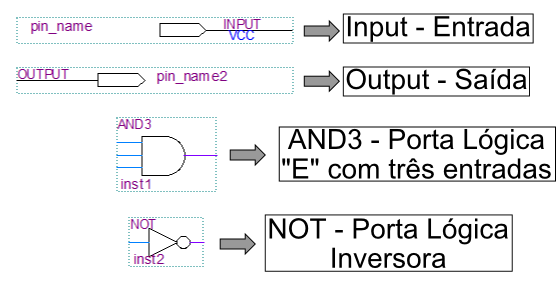

O significado dos símbolos usados pelo Quartus® II estão na Figura 2.

Figura 2: Legenda dos símbolos do Quartus® II

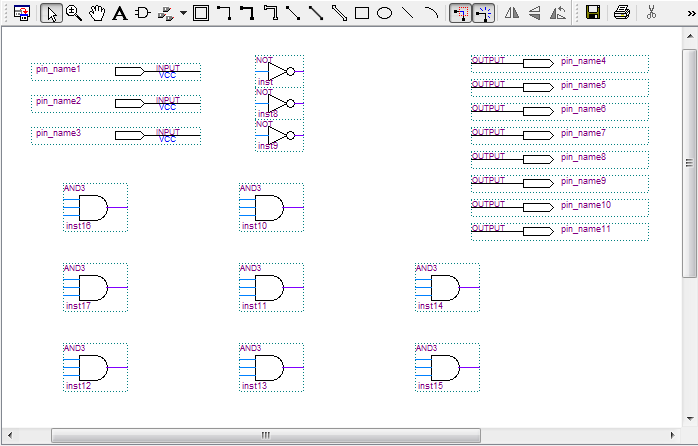

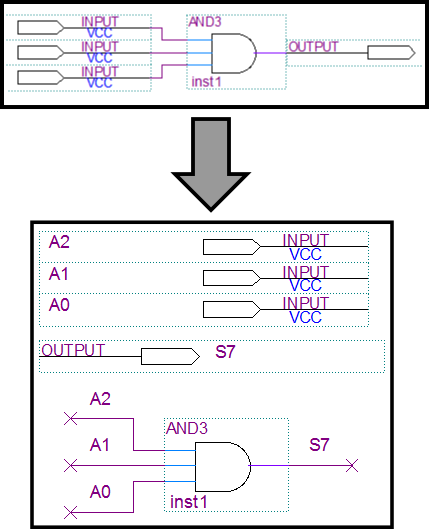

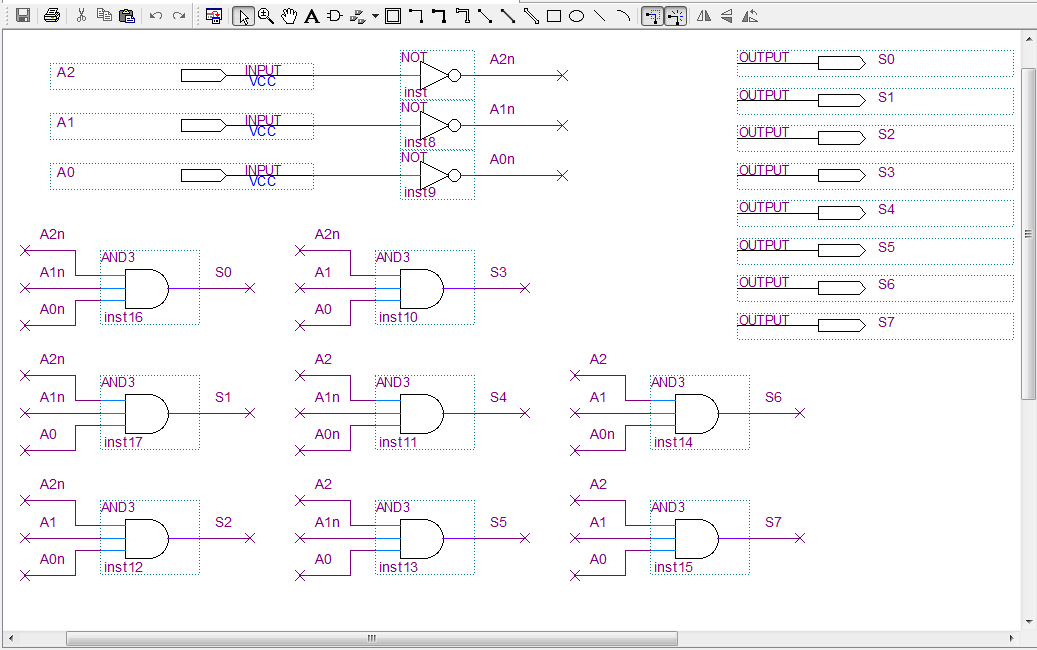

Com o programa, estruture o decodificador 3x8 em modo esquemático. Insira três entradas, oito saídas, três portas inversoras e oito portas "E" de três entradas, como ilustrado na Figura 3.

Figura 3: Preparo do Diagrama de Blocos no Quartus® II

Não será preciso desenhar as ligações dos terminais de entrada, porta inversora ou saída com as portas lógicas "E", pois conseguimos ligá-las nomeando seus terminais, ilustrado abaixo.

Figura 4: Ligação Nomeando os Terminais

Para aprender a implementar o projeto nesse software, veja o tutorial no final deste artigo (Tutorial: Projeto Simples com Entrada em Modo Esquemático). O diagrama final do projeto está na Figura 6, com seus terminais devidamente nomeados e desenhados.

Figura 5: Diagrama de Blocos no Quartus® II

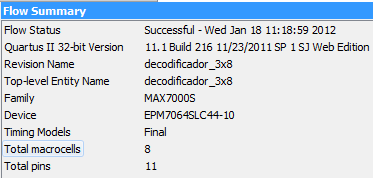

Depois de estruturar todo projeto, faça uma Análise e Síntese para poder simulá-lo, além do programa procurar algum erro ou aviso no esquemático. Para conhecer alguns deles e aprender a solucioná-los veja o tópico "Análise e Síntese" no tutorial ao final desse artigo. Um resumo da Análise e Síntese está logo abaixo.

Figura 6: Resumo da Análise e Síntese

Simulação

Como esse projeto foi feito em diagrama de blocos, precisamos converte-lo em um código VHDL para simulá-lo no software ModelSim®-Altera. A simulação foi realizada em modo interativo. Aprenda a converter o diagrama de blocos em VHDL e simular pelo modo interativo no tutorial do artigo sobre Simulação Interativa com o ModelSim-Altera.

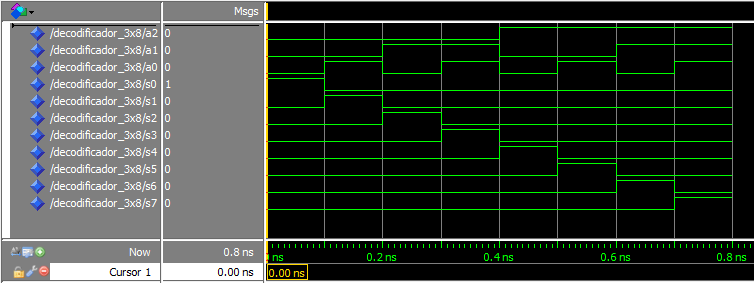

Na simulação, atribuímos níveis lógicos nas entradas e verificamos se os níveis lógicos das saídas estão de acordo com a lógica do projeto. Por exemplo, quando atribuímos "011", respectivamente em A2, A1 e A0, apenas a saída S3 ficará em nível lógico alto, enquanto todas as outras ficam em nível lógico baixo. A Figura 7 é o resultado da simulação em formas de onda.

Figura 7: Resultado da Simulação no ModelSim®-Altera

Estrutura Física

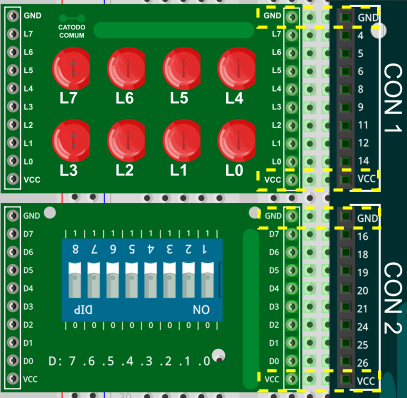

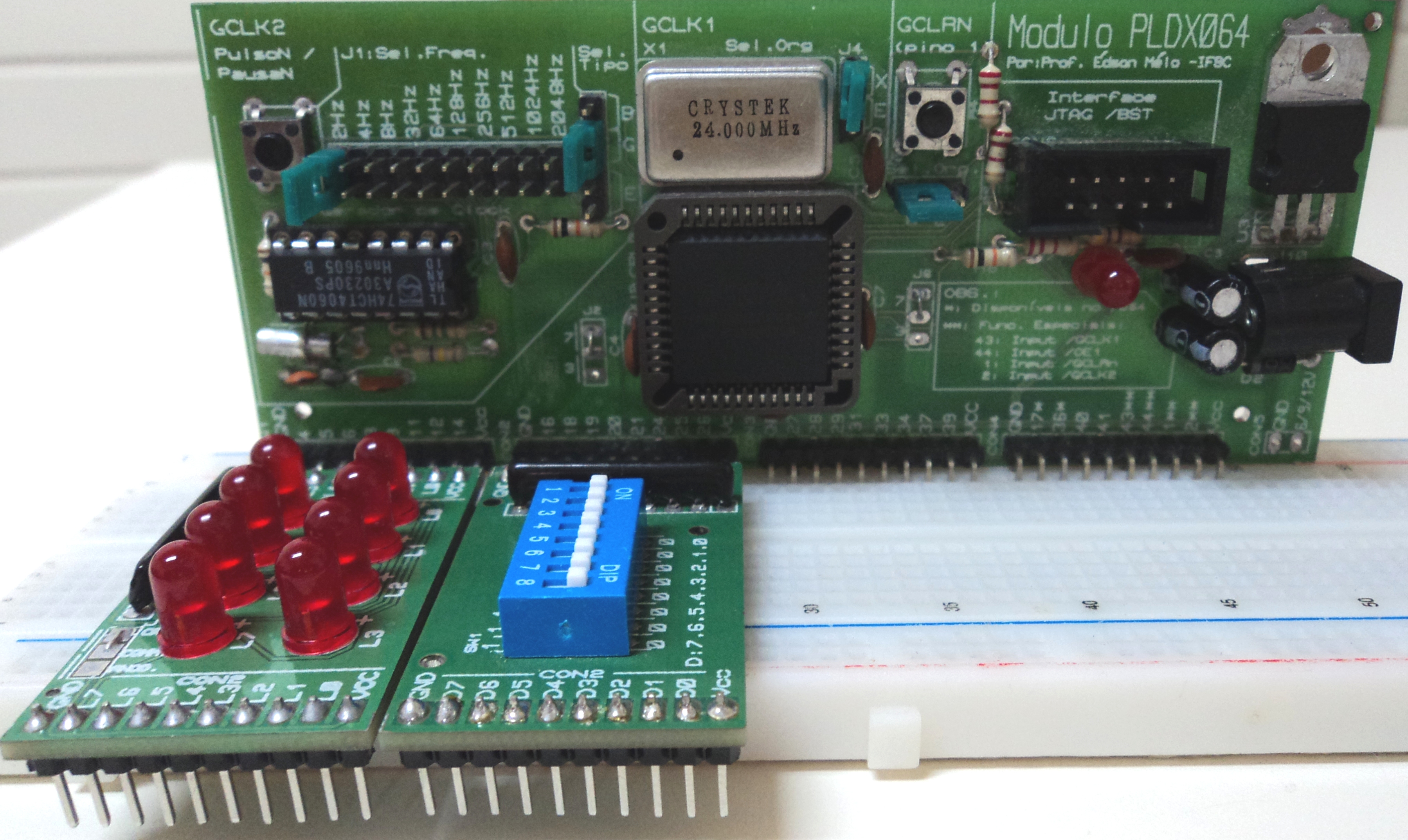

O projeto é composto pelo módulo de CPLD, uma placa de LEDs e outra de chaves, conectados respectivamente no CON1 e no CON2 do CPLD, como mostra a Figura 8. Lembre-se de que o CPLD usado é o EPM7064, da família MAX7000S.

No projeto, as entradas são implementadas pela placa de chaves, as saídas pela placa de LEDs e as funções lógicas pelo kit de CPLD.

Figura 8: Estrutura Física do Projeto

Montagem e Roteamento

Fique atento para que o Vcc e o GND dos periféricos fiquem alinhados com o do CPLD. Veja em detalhe a montagem do projeto na Figura 9, feita no Fritzing.

Figura 9: Ligação na Matriz de Contatos

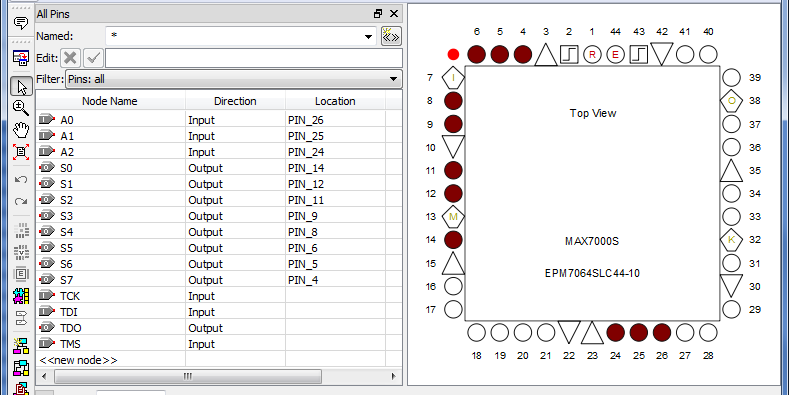

A Figura 10 ilustra a pinagem atribuida no Pin Planner, de acordo com a ligação na matriz de contatos.

Figura 10: Atribuição dos Pinos no Pin Planner

Gravação e Teste

Depois de implementar e atribuir os pinos do projeto, faça uma "Compilação Completa" para gerar o arquivo de gravação do projeto, além do programa procurar algum erro ou aviso no mesmo.

Para gravar o projeto siga o tutorial na etapa de "Gravação do CPLD". Lembre-se sempre de gravar o módulo de CPLD separadamente dos periféricos, evitando problemas na pinagem atribuida em projetos anteriores.

Tutorial - Implementando o Projeto

Segue abaixo o tutorial sobre a implementação do projeto e para ampliá-lo clique aqui, ou sobre ele.

Tutorial: Projeto Simples com Entrada em Modo Esquemático

Arquivos do Projeto

Para o download do projeto completo, clique aqui.

O arquivo está no formato "zip", e inclui, entre outros:

- O arquivo de projeto do Quartus , no formato ".qpf"

- O projeto em modo esquemático , no formato".bdf"