VGA para FPGA

- Detalhes

- Categoria: Exemplos com FPGA

- Publicado em Quarta, 26 Outubro 2011 08:33

- Escrito por Andre Vinicius Rocha Silva

- Acessos: 6920

VGA para FPGA

Figura 1 - Foto do projeto.

Nesta página será apresentado um método de apresentar imagens de um FPGA para um monitor através de uma porta VGA. Para tal tarefa, será feita uma breve explicação do funcionamento da sincronização VGA, um método de enviar imagens e ler ler a memória. Uma vez implementado, o projeto permite apresentar qualquer imagem, desde que esteja no formato adequado, isto nos permite uma grande variedade de aplicações.

Figura 2 - Imagem mostrada na tela

O projeto a seguir é um exemplo de circuito lógico sequencial, descrito em VHDL e simulado no software ModelSim®-Altera, através de um test bench.

Os dispositivos necessários para a implementação do projeto são:

- Uma placa ALTERA DE0.

- Uma interface serial-VGA.

- Um monitor com entrada VGA.

Funcionamento da porta VGA

Sincronização

Uma tela no modo VGA é dividida em linhas, cada linha é dividido em pontos (pixels). Geralmente a tela 480 linhas e cada uma com 640 pixels que só podem ser acesos um por vez. Para formamos uma imagem, usamos o efeito da persistência da visão, também usado no projto Multiplexação de 6 algarismos.

Para "enganar" a visão, faremos o monitor apresentar 60 quadros a cada segundo (60 hz), por isso deveremos sincronizar o FPGA com o mesmo, para podermos controlar o que será apresentado.

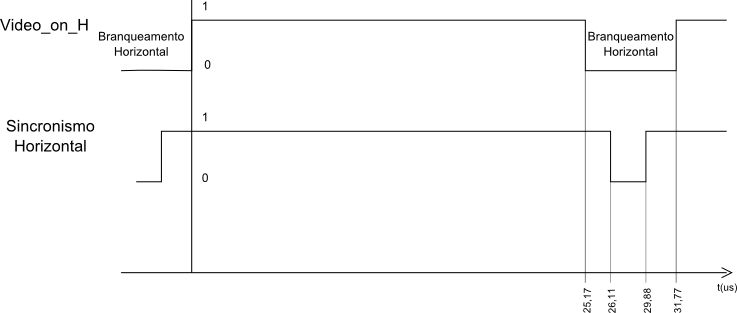

Para a sincronização com o monitor, precisamos enviar dois pulsos de sincronismo um vertical e um horizontal. O horizontal, apresentado na Figura 2, indica para o monitor que acabou a linha na qual ele estava mostrando os pixels e que ele deve passar para a próxima.

Figura 3 - Sincronismo Horizontal

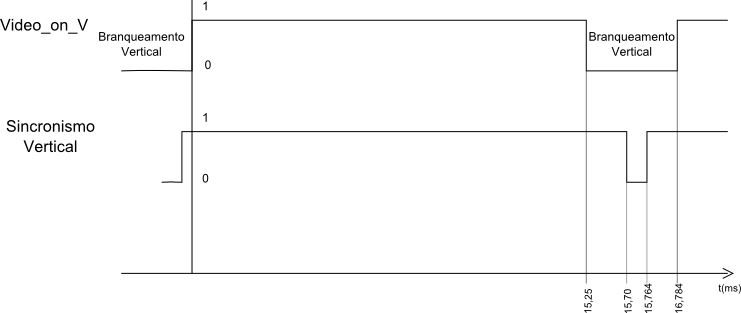

O vertical, apresentado na Figura 3, indica para o monitor que acabou a tela e que ele deve começar a próxima.

Figura 4 - Sincronismo Vertical

Cada pixel apresentará 12 bits para a cor, no modelo RGB que serão enviados através da porta.

Para mais informações sobre o funcionamento da porta VGA , clique aqui.

VGA para FPGA

Blocos do projeto

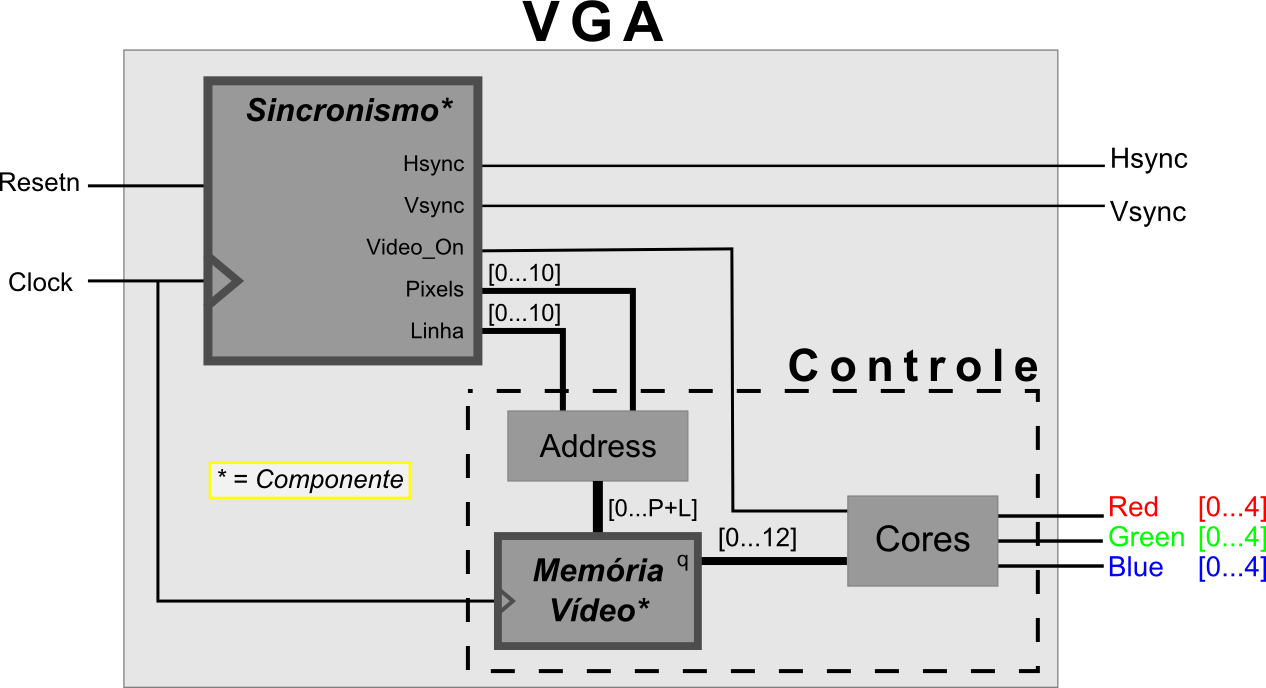

Para facilitar o entendimento, o projeto foi dividido em componentes como mostra a Figura 5.

Figura 5 - Blocos do projeto

Sincronismo

Componente que envia os sinais de sincronismo para o monitor.

O componente possui um contador de pulsos de clock para marcar o tempo. A DE0 possui um clock de 50MHz, fazemos a contagem de pulsos até completar uma linha, seguindo os tempos de sincronismo apresentados na Figura 3.

|

Tempo(us) |

Pulsos de Clock |

| 25,17 | 1258 |

| 26,11 | 1306 |

| 29,88 | 1494 |

| 31,77 | 1588 |

O trecho de código abaixo, apresenta o método utilizado para a sincronização dos sinais responsáveis pelo sincronismo horizontal.

Quando a contagem chega ao fim da linha incrementa-se a contagem de linhas. Os sinais de sincronismo são enviados de acordo com os tempos apresentados na Figura 4.

|

Tempo(ms) |

Contagem de Linhas |

| 15,250 | 479 |

| 15,700 | 495 |

| 15,764 | 496 |

| 16,764 | 528 |

O trecho de código abaixo, apresenta o método utilizado para a sincronização dos sinais responsáveis pelo sincronismo vertical.

Esse componente também envia a posição que está sendo escrita no monitor.

Memória

A memória foi implementada através de uma megafunção da Altera.

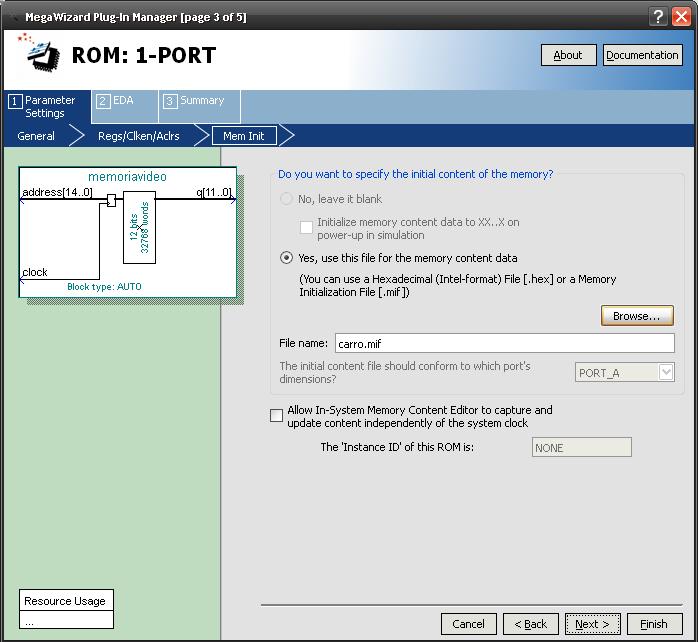

Na memória, está um arquivo .mif(Memory Initialization File) que possui o mapeamento da imagem a ser mostrada na tela. O arquivo .mif é indicado através do MegaWizard, como mostra a figura a Figura 6.

Figura 6 - Janela da Megafunção.

O número de bits para o endereço é igual a quantidade de bits do número de pixels que quer se mostrar mais o número de bits de Linhas a serem mostradas [P+L].

VGA

Parte das variáveis Pixels e Linhas,recebidas do componente Sincronismo, são enviadas pro componente Memória o tamanho do endereço:

Implementação do Projeto

Análise e Síntese

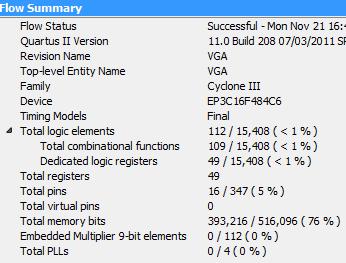

A Figura 7 apresenta o resultado da Análise e Síntese do projeto.

Figura 7 - Resultado da Análise e Síntese

Pinagem

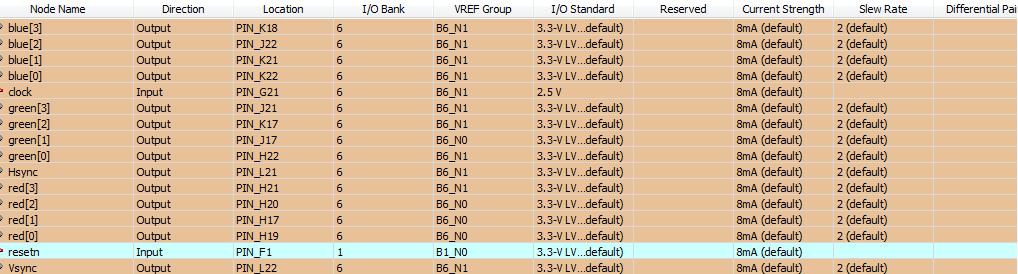

Os pinos devem ser selecionados da seguinte forma:

Figura 8 - Pinagem do projeto

Clique na imagem para ampliá-la.

O utilizador deve estar atento à tensão de saída, a mesma deve ser ajustada, caso contrário, se permanecer em 2,5V o monitor parecerá meio apagado.

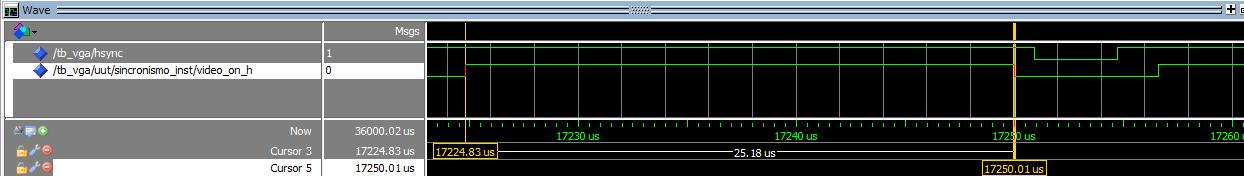

Simulação

O Testbench simula 3600000 pulsos de clock e mantém o Resetn em '1'.

As Figuras abaixo apresentam os tempos que foram simulados.

Clique nas imagens para ampliá-las.

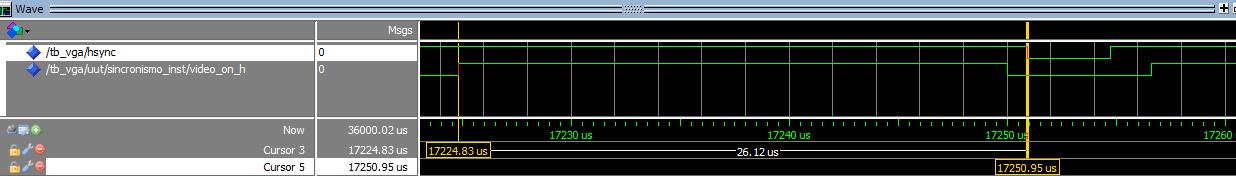

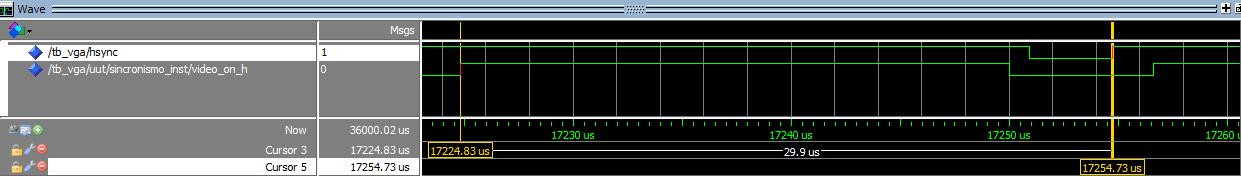

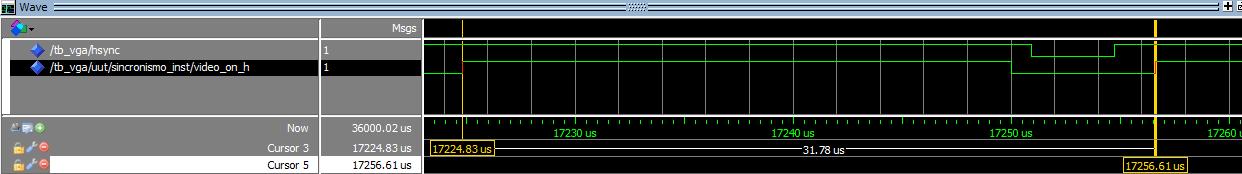

Sincronismo Horizontal:

Tempo de descida HSYNC

Tempo de descida HSYNC

Tempo de subida HSYNC

Tempo de subida HSYNC

Tempo de subida VIDEO_ON_H

Tempo de subida VIDEO_ON_H

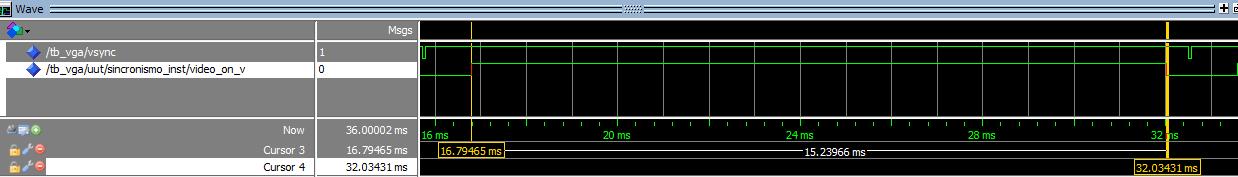

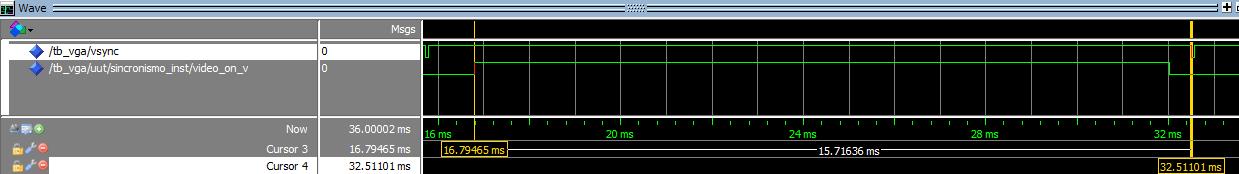

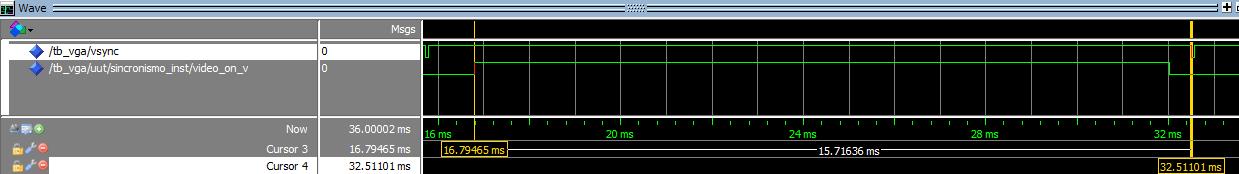

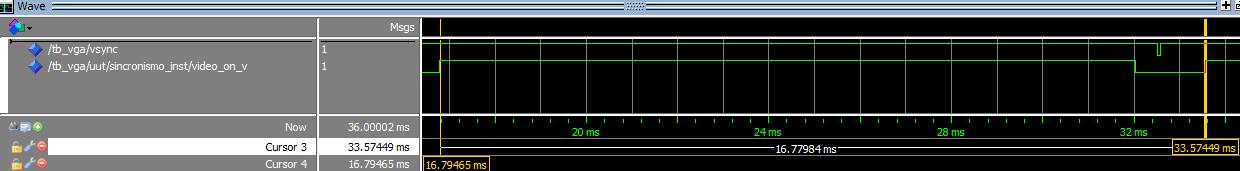

Sincronismo Vertical:

Tempo de descida VIDEO_ON_V

Tempo de descida VIDEO_ON_V

Tempo de descida VSYNC

Tempo de descida VSYNC

Tempo de subida VSYNC

Tempo de subida VSYNC

Tempo de subida VIDEO_ON_V

Tempo de subida VIDEO_ON_V

Arquivos do Projeto

Para o download do projeto completo, clique aqui.

O arquivo está no formato "zip", e inclui, entre outros:

- O arquivo de projeto do Quartus , no formato ".qpf"

- A descrição no formato VHDL , no formato".vhd"