Multiplexação Display de 6 Algarismos

- Detalhes

- Categoria: Exemplos com CPLD

- Publicado em Quinta, 11 Agosto 2011 15:18

- Escrito por Andre Vinicius Rocha Silva

- Acessos: 5120

Controle de display multiplexado

O projeto descrito a seguir é um exemplo de circuito sequencial descrito em VHDL e simulado no software Modelsim-Altera®, através do modo interativo.

A lógica deste projeto pode ser alterada de forma a funcionar como componente para projetos mais complexos.

Serão utilizados nesse projeto:

- 1x kit CPLD_7064;

- 1x Placa de Display de 6 Algarismos.

Lógica de Funcionamento

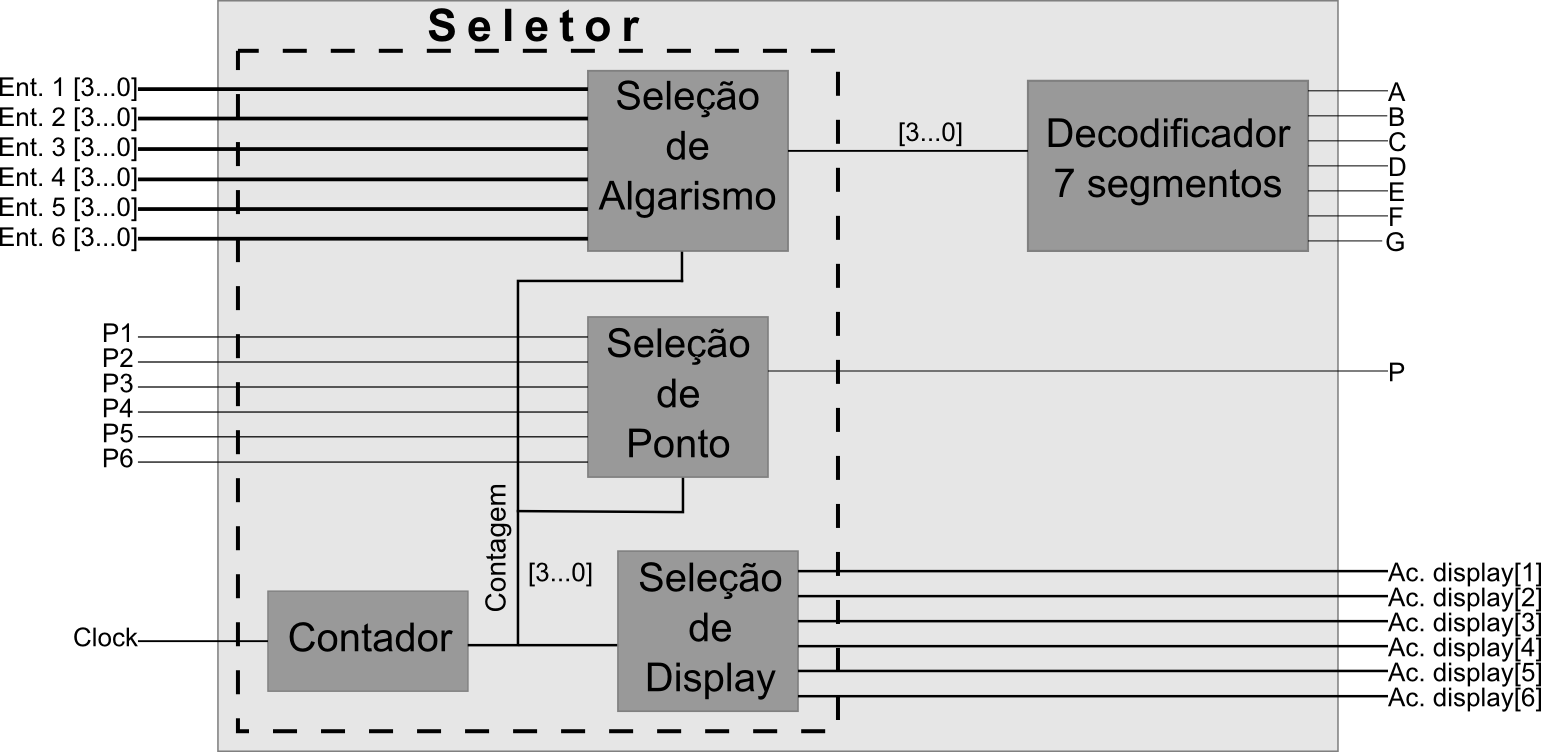

A lógica do projeto é composta pelos seguintes blocos:

Figura 1 - Blocos da lógica.

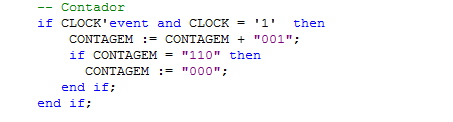

Um contador que a cada pulso de clock incrementa a variável contagem. Esta variável é incrementada até seu valor chegar a 5, então ele volta a 0. Se fosse necessário acender menos displays, poderia-se diminuir o valor máximo da contagem. Por exemplo de 0 a 3 acenderia apenas 4 algarismos.

Figura 2 - Contador em VHDL.

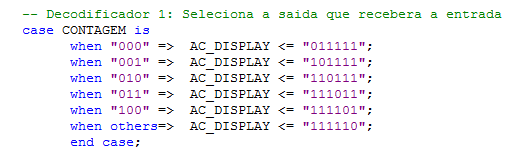

Um decodificador que a partir do valor atual da variável contagem seleciona o display que será acionado.

Figura 3 - Decodificador para o acionamento.

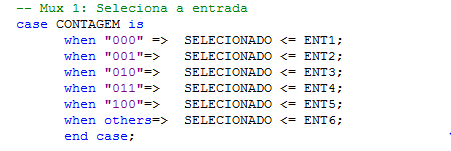

Um multiplexador que seleciona, a partir do valor atual da variável contagem, seleciona qual entrada será enviada para o display selecionado pelo decodificador.

Figura 4 - Multiplexador do valor de saída.

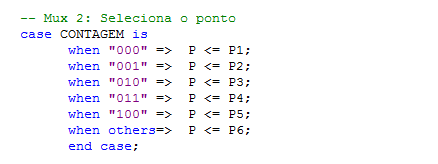

Um multiplexador que seleciona o estado do ponto a partir do valor da contagem.

Figura 5 - Multiplexador o valor do ponto.

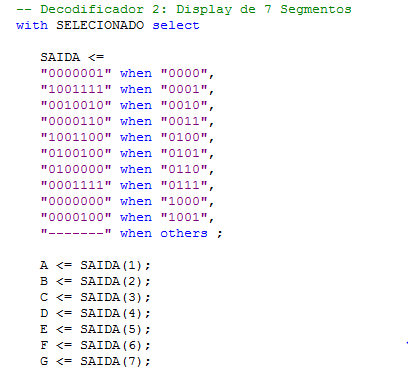

Um decodificador para display de 7 segmentos que recebe a entrada selecionada, e envia para o display acionado apresentar na forma decimal.

Figura 6 - Decodificador para um display de 7 segmentos.

Estes componentes funcionarão juntos conforme mostra a animação, clique na imagem para vê-la:

Animação 1 - Funcionamento da lógica.

Análise e Síntese

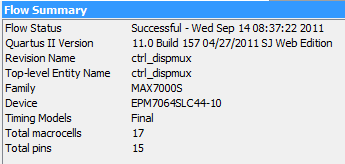

Depois de descrito todo o projeto, é necessário fazer uma análise para detectar possíveis erros e poder simulá-lo.

A Figura 7 mostra o resultado da análise.

Figura 7 - Resultado da análise e síntese.

Simulação

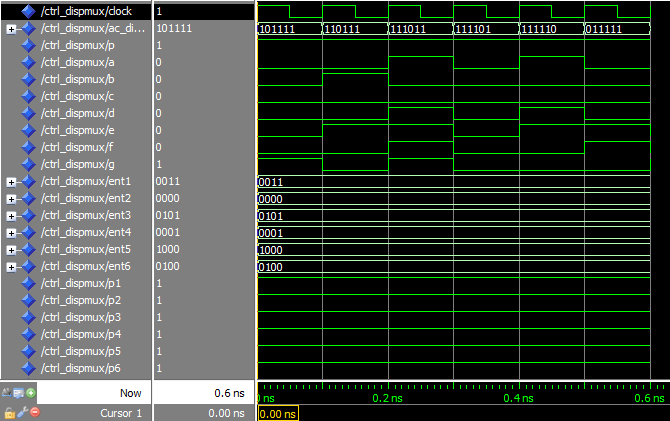

A Figura 8 mostra o resultado da simulação feita no Model-Sim Altera. Foram simulados apenas 6 pulsos de clock, pois passou por todos os 6 displays de 7 segmentos. O processo fica se repetindo.

Informações sobre o software e seu uso, clique aqui

Figura 8 - Simulação do projeto

Estrutura Básica do Sistema

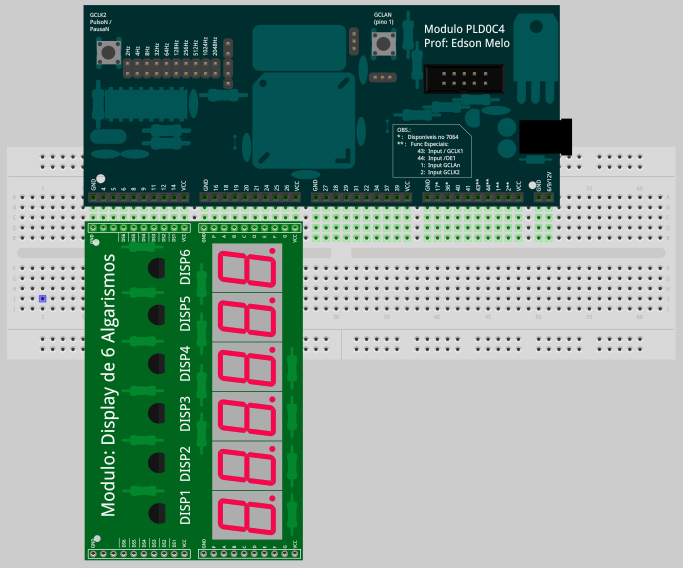

O sistema é composto por:

- Um módulo de CPLD

Que deverá ser configurado para usar o sinal de clock de aproximadamente 256 Hz, gerado pelo oscilador de baixa frequência.

Para informações sobre seu funcionamento, clique aqui

- Um display de 6 algarismos

Que será montado junto ao módulo de CPLD, respeitando a pinagem definida no projeto.

Para informações sobre seu funcionamento, clique aqui

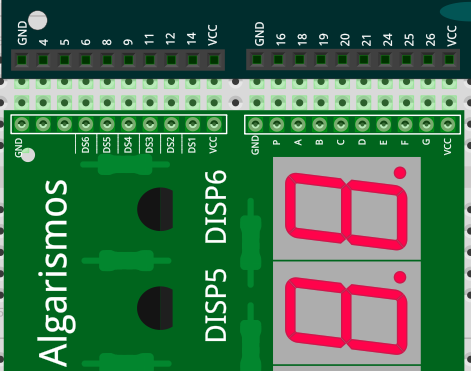

Os componentes serão montados como mostram as Figuras 9 e 10.

Figura 9 - Esquema do projeto no Fritzing.

Figura 10 - Detalhe da montagem

A Tabela 1 mostra como deve ser ajustada a pinagem do projeto.

Figura 11 - Pinagem do projeto.

Arquivos de Projeto

Para o download do projeto, clique aqui.

O arquivo está no formato "zip", e inclui, entre outros:

- O arquivo de projeto do Quartus , no formato ".qpf"

- A descrição no formato VHDL , no formato".vhd"