Display de 7 Segmentos Registrado

- Detalhes

- Categoria: Exemplos com CPLD

- Publicado em Terça, 22 Maio 2012 08:19

- Escrito por João Marcos de Aguiar

- Acessos: 5092

Display de 7 Segmentos Registrado

O presente projeto é um exercicio relacionado a declaração e uso de flip-flops em VHDL. Esse projeto foi elaborado com base em um exercicio feito durante a aula de laboratório de Sistemas Digitais, ministrada na UFSC (Universidade Federal de Santa Catarina) pelo Professor Doutor Eduardo Augusto Bezerra.

O projeto foi desenvolvido em VHDL, bem como o testbench para a simulação, feita no ModelSim-Altera.

Componentes utilizados:

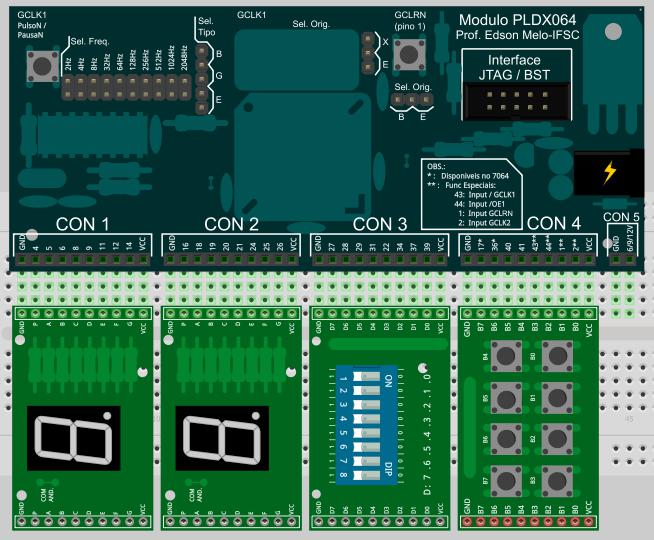

- 1x Kit CPLD_7064;

- 1x Placa de Botões;

- 2x Placa de Display de 7 segmentos;

- 1x Placa de Chaves;

Descrição do Funcionamento

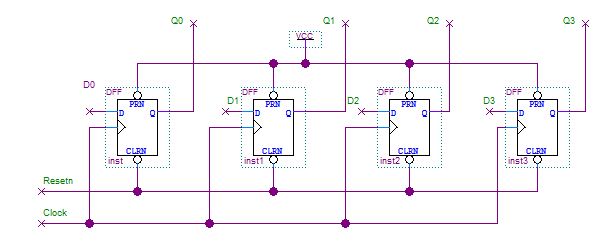

Os Flip-Flops são elementos sincronos de memória, ou seja, só atualizam seu valor de saída quando há uma variação no clock (borda de subida ou borda de descida). O agrupamento de flip-flops é chamado de registrador. Nesse projeto será utilizado um registrador de 4 bits, ou seja, um grupo de 4 flip-flops.

Figura 1: Conjunto de Flip-Flops, formando um registrador de 4 bits.

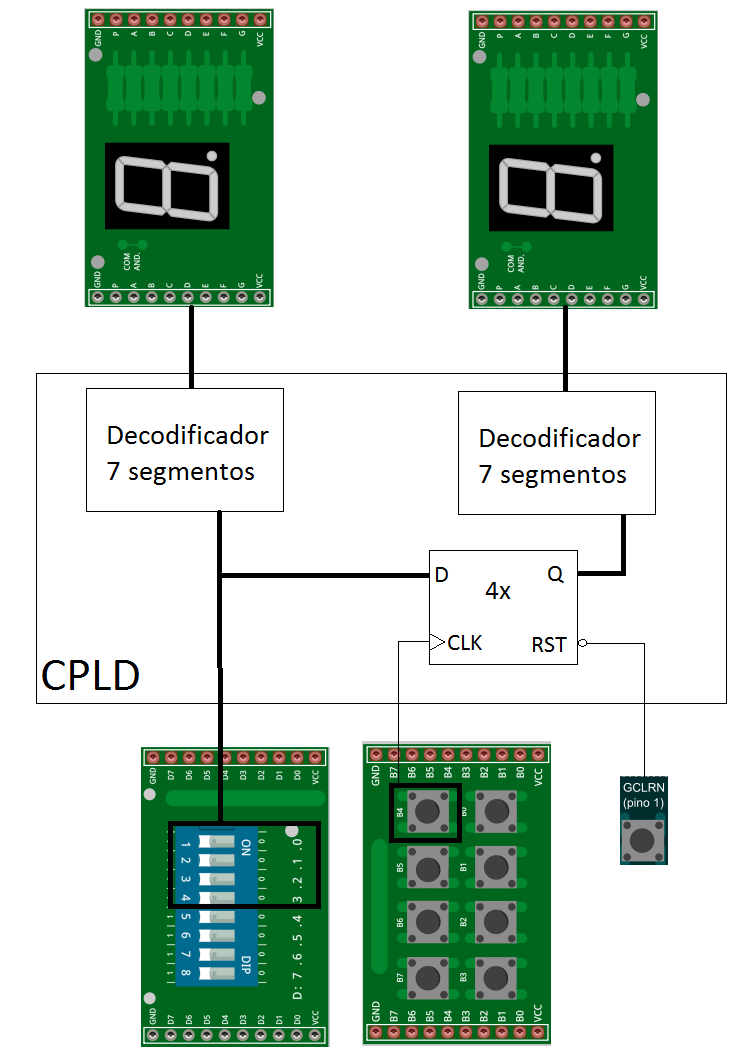

O projeto fará a decodificação para dois displays de 7 segmentos, com um dado de quatro bits de entrada. Isso será feito, fazendo com que um dos displays apresente diretamente o valor no dado de entrar e o segundo display só será atualizado quando houver um pulso no Clock dos flip-flops (neste caso será utilizado um botão para o clock). A figura abaixo ilustra o funcionamento do projeto:

Figura 2: Circuito a ser montado.

Projeto em VHDL

Para a implementação do projetos proposto, precisamos primeiramente ver com fazer a declaração de um Flip-Flop em VHDL comportamental. A estrutura abaixo é uma declaração de um flip-flop, onde d é um sinal de um bit de entrada e q a saída de um bit:

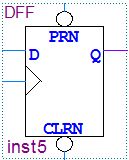

O código é equivalente a um flip-flop do tipo D sem preset.

Figura 3: Flip-Flop do tipo D com preset.

Para expandir a quantidade de flip-flops,basta mudar a declaração dos sinais de entrada e saída para um vetor com o número desejado de bits. Utilizaremos declaração (3 downto 0) para declarar os sinais. Abaixo está declarada a entidade do projeto. As saídas serão apenas os segmentos dos displays, a saída dos flip-flops serão ligadas ao decodificador para display de 7 segmentos. O clock utilizado será um botão, que possibilitará a escolha do número a ser armazenado.

Dentro da arquitetura, apenas teremos um sinal Q, que será a saída do registrador. Como explicado anteriormente, a estrutura para a declaração do registrador é similar a declaração do flip-flop, a única diferença é que os sinais utilizados agora possuem mais de um bit.

Como temos dois displays, utilizaremos dois decodificadores, com a mesma estrutura, sendo a única diferença os sinais utilizados. Abaixo está apresentado uma das estruturas. Para montar a outra estrutura basta trocar Q por DADO e DISP_7SEG_2 por DISP_7SEG_1.

Simulação

A simulação deste projeto se baseia na inserção de dados na entrada DADO e emulação do pressionamento do botão para o registro do dado que será mostrada no segundo display. Para simulação, será preciso apenas emular alguns valores na entrada DADO e o acionamento do botão e verificar o funcionamento. Poderia ser feito o teste de todas as possibilidades para o valor de dado, mas como o decodificador é identico ao Decodificador para Display de 7 Segmentos, onde foi testada todas as possibilidades, não será necessário emular todos os valores.

O código abaixo apresenta o comportamento do testbench implementado:

Os nomes utilizados no testbench foram os mesmos utilizados no projeto, lembrando que isso não é necessário e a atribuição depende da ordem em que aparece no projeto e na declaração de UUT. O resultado da simulação pode ser visto abaixo na janela do ModelSim-Altera:

Figura 4: Resultado da simulação.

Estrutura Física

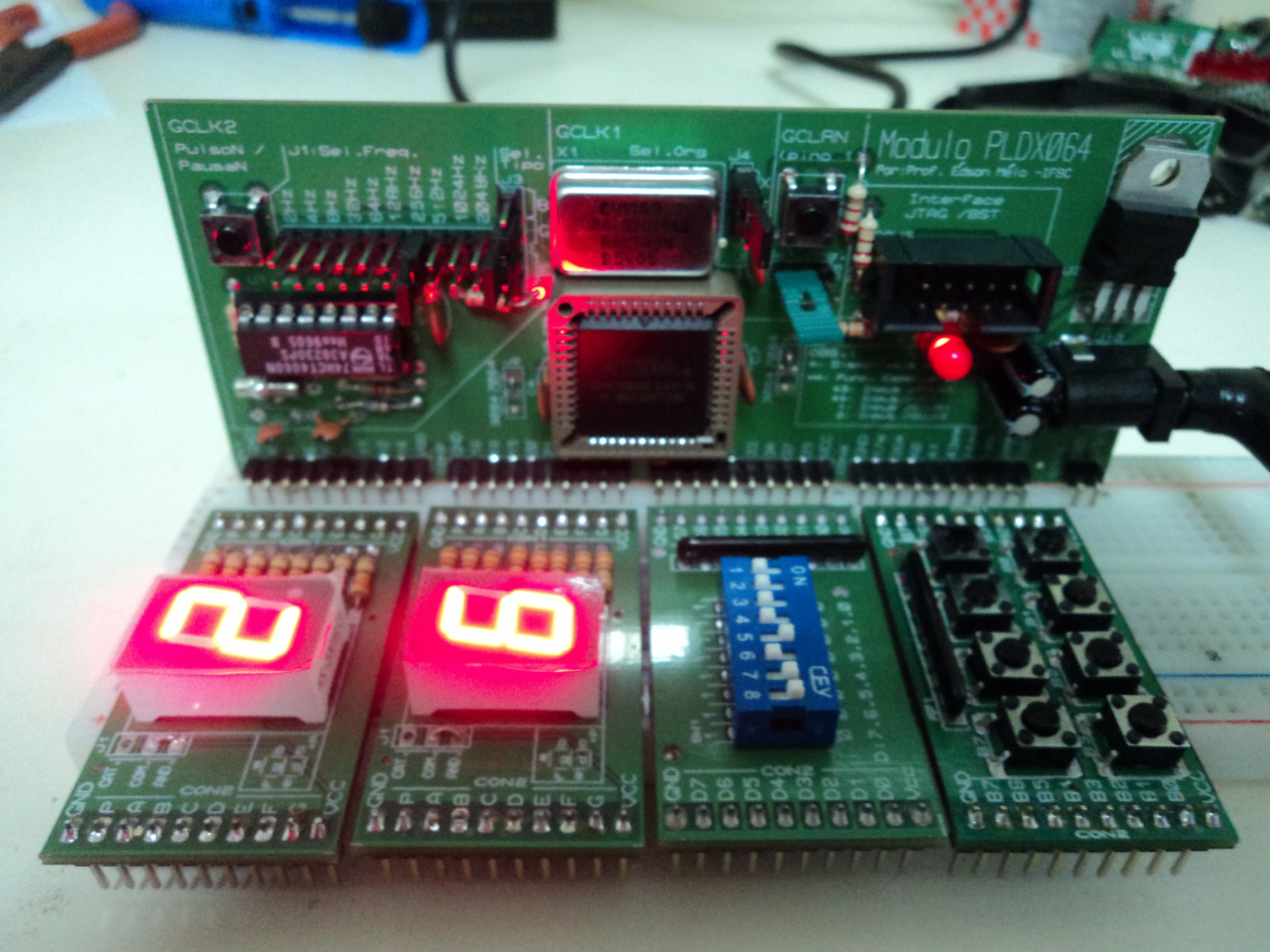

Figura 5: Circuito montado e funcionando.

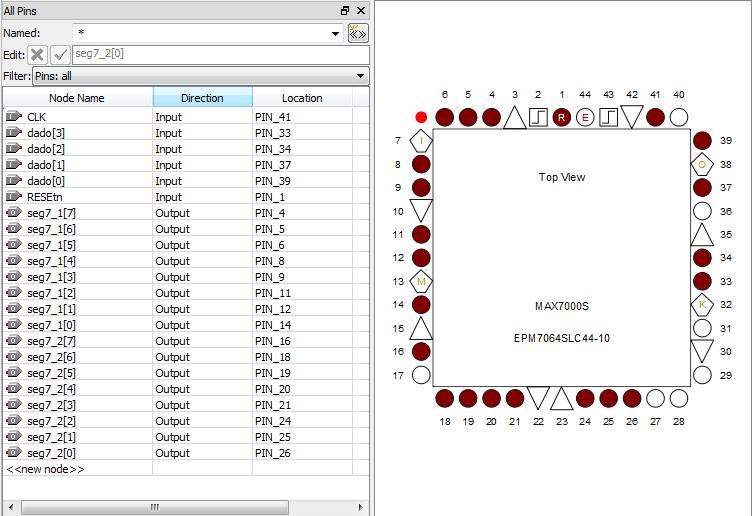

O projeto foi implementado pensando na utilização do Kit CPLD_7064, onde o será gravado o projeto. Nas portas CON1 e CON2 serão conectados placas de display de 7 segmentos, na porta CON3 será conectada uma placa de chaves e na porta CON4 será conectada a placa de botões, que pode ser subistituída pelo botão de clock de baixa frequência, caso deseje-se utilizar mais algum periférico no projeto. O CPLD utilizado é o EPM7064 da família MAX7000S

Montagem e Roteamento

A montagem pode ser feita como na ilustração abaixo, feita no Fritizing:

Figura 6: Ilustração da montagem no Fritizing.

Com base na montagem feita e na pinagem da placa, podemos definir a pinagem do componente:

Figura 7: Pinagem atribuida para o projeto.

Gravação e Teste

Para a gravação do projeto, basta seguir as instruções dadas no tutorial. O teste é feito montando os periféricos junto ao kit CPLD e testando a inserção de dados.