Gerador de Sinal PWM

- Detalhes

- Categoria: Exemplos com CPLD

- Publicado em Terça, 02 Julho 2013 10:19

- Escrito por Eduardo Luz

- Acessos: 3607

GERADOR DE SINAL PWM COM O KIT PLD7064.

Resumo

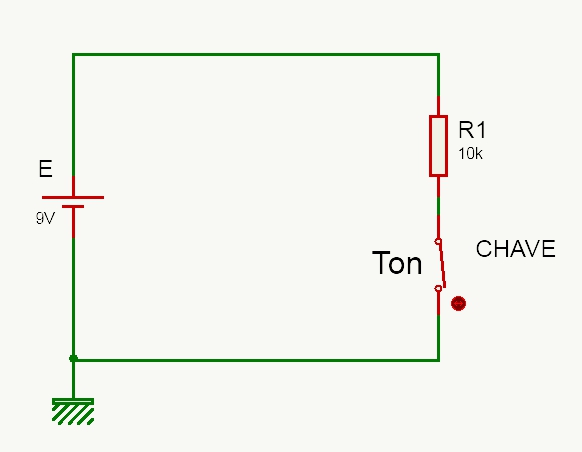

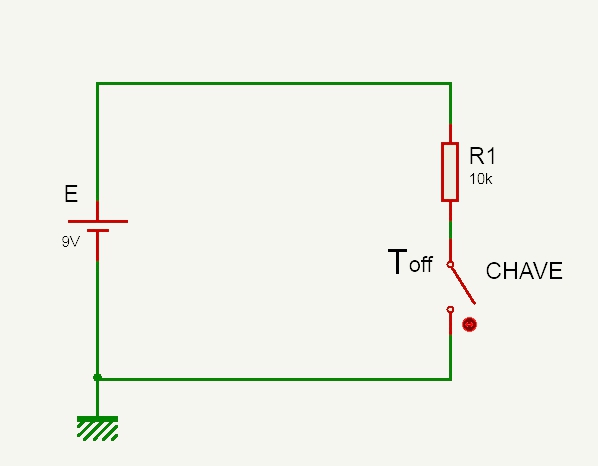

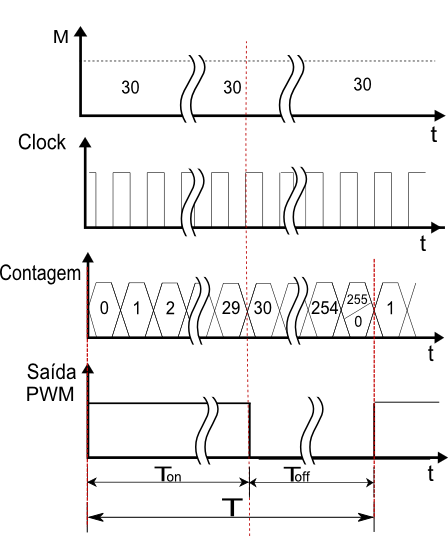

A modulação por largura de pulso (PWM, de "Pulse Width Modulation") é uma técnica largamente utilizada para o controle de dispositivos e sinais, desde iluminação e acionamento de motores até áudio. Em sua forma mais simples, o PWM implica no chaveamento da entrada do circuito (alimentação ou sinal), como mostrado na figura abaixo, para uma carga resistiva R1. Se a chave, no circuito mostrado, conduz durante um intervalo Ton, a seguir bloqueia durante um intervalo Toff, e a soma destes intervalos corresponde a um período T de funcionamento do sistema, a tensão média na carga vale:

O parâmetro D é denominado razão cíclica da onda, e desde que Ton é maior ou igual a 0, e menor ou igual a T, então D está compreendido no intervalo [0,1], ou seja, entre 0% e 100%. Naturalmente, a tensão média de saída no circuito acima, está entre 0% e 100% da tensão de entrada.

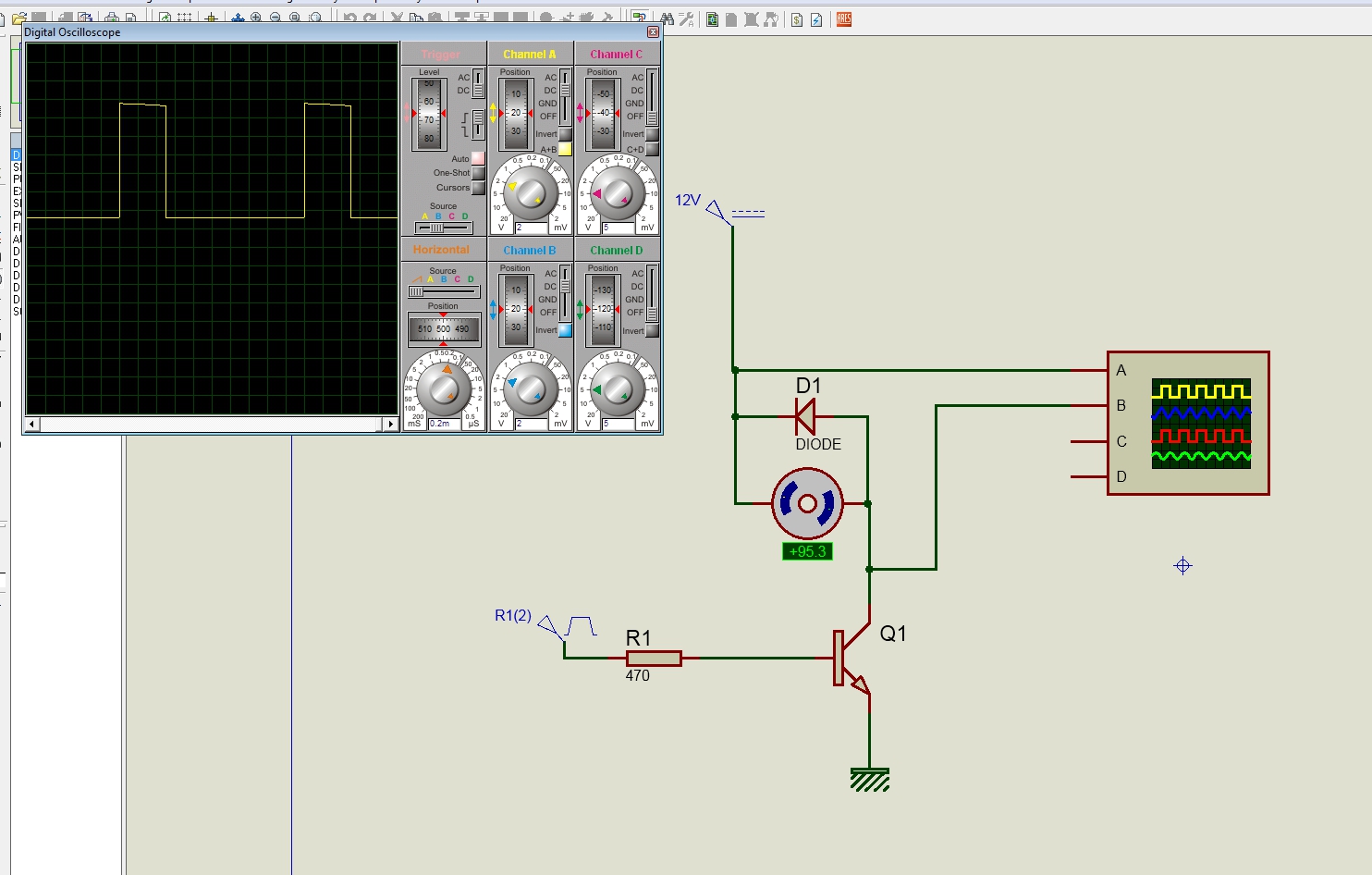

Em aplicações práticas comuns, PWM pode ser usada no acionamento de motores ou outras cargas indutivas, e neste caso é necessário um circuito de proteção (D1, diodo de roda livre) contra sobretensão no transístor, como mostrado na figura abaixo. (download do arquivo para simulação no Proteus)

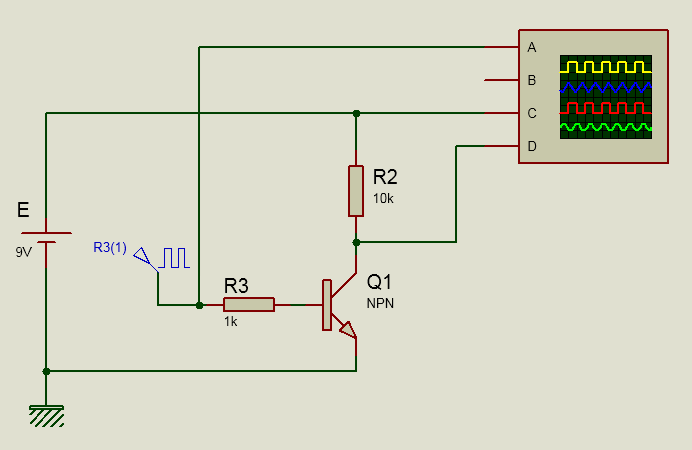

A figura abaixo mostra o diagrama esquemático (download) de um circuito simples de carga resistiva que não necessita circuito de proteção, que pode ser simulado no Proteus mesmo na versão de demonstração.

Neste artigo foi implementado um gerador de onda PWM, para o kit PLD7064, e verificamos o seu funcionamento com o uso de instrumentação simples e no acionamento de um LED. O circuito projetado é bastante versátil permitindo ampla variação da frequência de saída, até 94 KHz com o “clock” de 24 MHz do kit, e ajuste da razão cíclica com uma resolução 0,39% (corresponde ao incremento de uma unidade na contagem de 0 a 255)

Introdução

Uma forma simples de geração de PWM com um circuito digital é fazer a contagem dos pulsos de um sinal de “clock”, até certo valor máximo, e fazer um sinal de saída (a onda PWM desejada) ficar em nível alto durante uma parte inicial (ou final) da contagem, até certo valor dela, como ilustrado na figura seguinte. No caso apresentado, a contagem está sendo comparada com o valor que determina a largura do pulso alto desejado. Observe que a saída vai a nível alto no início da contagem, e volta a '0' quando a contagem atinge aquele valor de comparação.

Se uma contagem de oito bits é executada, variando de "00000000" a "11111111" ( 0 a 255, em decimal), tem-se 256 possíveis valores de comparação. Com um projeto adequado, a razão cíclica nula (0%) poderia corresponder a um valor de comparação de 0, e a razão cíclica 100% corresponderia ao valor de 255 ("11111111"). No sistema proposto, a contagem é anulada imediatamente ao chegar a 255, e assim uma onda completa na saída corresponde a 255 períodos de "clock", não a 256.

A frequência do sinal PWM deve ser adequada ao uso que se fará dele. Podem-se desejar altas frequências no acionamento de transístores MOSFET em fontes chaveadas, ou em aplicações de áudio, ou baixas frequências (até dezenas de KHz) no acionamento de pequenos motores com transístores bipolares. No projeto proposto, utiliza-se um contador de oito bits com função de "prescaler", ou divisor de frequência. Através da contagem até certo valor de referência, quando aquela contagem é zerada novamente, pode-se dividir a frequência do “clock” por um valor N, até 256. Para isto, aplica-se (N - 1), ou seja, um valor entre 0 e 255 como entrada de controle no bloco de “prescaler”.

Finalmente, para dar alguma flexibilidade adicional ao projeto, utilizou-se um bloco de controle de saída que permite inverter o PWM gerado, e também deixar a saída em alta impedância.

O projeto deverá ser implementado como um módulo de PWM, a ser utilizado como está, ou como bloco de projetos mais complexos, que serão apresentados brevemente neste portal.

Implementação do Módulo PWM em VHDL

Descrevemos aqui, basicamente, partes do código em VHDL que implementa o módulo PWM para CPLD.

Inicialmente, apresentamos abaixo o trecho de VHDL de declaração as bibliotecas .

O segundo trecho é a declaração da entidade ("entitiy"), com a declaração dos sinais de entrada e saída do projeto.

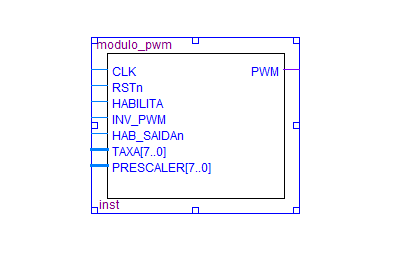

Entenda que a entidade define a interface de aplicação do bloco, e corresponde ao símbolo mostrado na figura seguinte:

No trecho de VHDL seguinte, o processo rotulado "gera_prescaler" conta os pulsos de “clock” de entrada, e gera o sinal PRESC_ENABLE, que habilita o bloco de PWM uma vez a cada N pulsos de “clock”. É este mecanismo que permite reduzir a frequência do PWM. Se a entrada “PRESCALER” é 0 ("00000000", ou X"00" para o formato “std_logic_vector” de oito bits), PRESC_ENABLE é sempre alto, e todo pulso de “clock” aciona o gerador de PWM.

Finalmente, abaixo, mostramos o processo que gera o PWM, a partir dos pulsos de “clock” de entrada, quando habilitado pelo PRESC_ENABLE, e com a razão cíclica determinada pela entrada TAXA.

Simulação Funcional

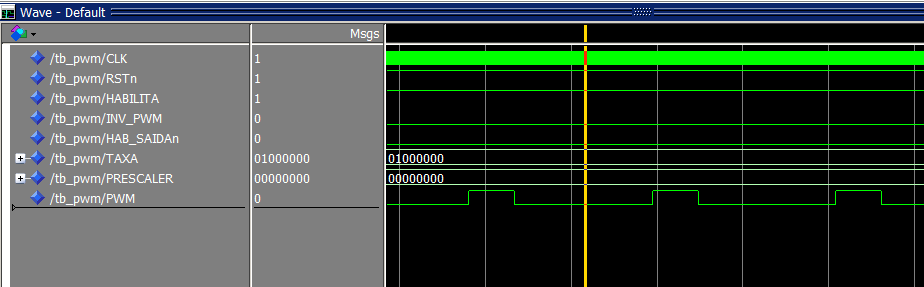

Para uma primeira verificação do funcionamento do sistema, desenvolvemos um "testbench" simples, que simula o seu comando, em algumas situações de razão cíclica e de “prescaler”. Utilize este “testbench” como ponto de partida para outros testes, e para obter uma melhor compreensão do módulo gerador de PWM. Apresentamos aqui trechos do arquivo, que está disponível no projeto completo para "download".

Dois processos simples compõem a arquitetura do “testbench”. No primeiro, um sinal de “clock“ de 24 MHz (ou seja, um período de aproximadamente 42 ns) é gerado.

Abaixo, mostramos um pequeno trecho da simulação, e de forma de onda resultante no PWM.

Implementação e Testes

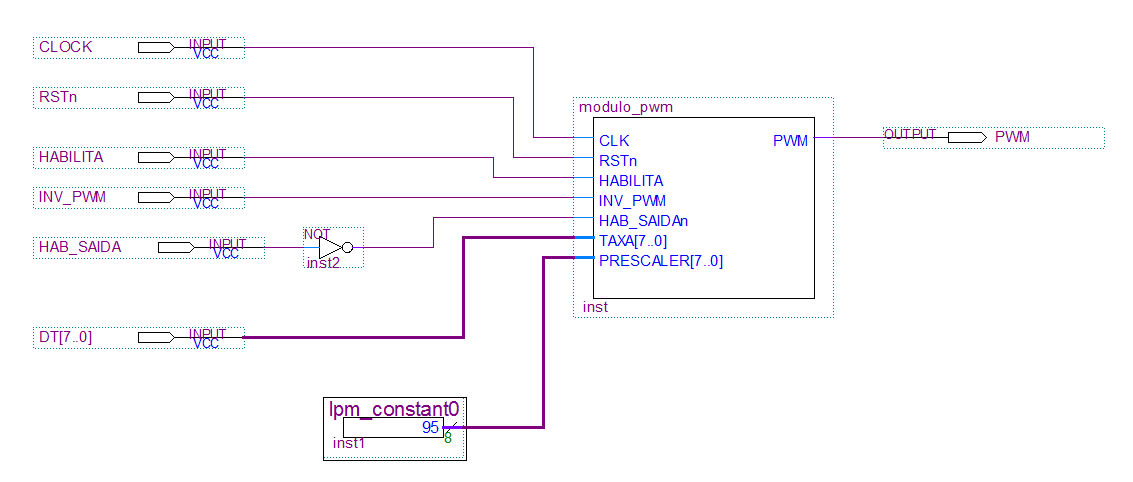

Para um teste mais prático do módulo de PWM, apresenta-se aqui um implementação dele como um bloco de um projeto em modo de diagrama esquemático do Quartus II, gerador de um PWM de frequência fixa de aproximadamente 1 KHz. Para isto, utiliza-se um fator de “prescaler” de 95. Este valor é aproximado, obtido pela divisão de 24 MHz por 255, e pela frequência desejada, de 1000 Hz:

24 MHz /255 /1 kHz = 94.11

A partir do arquivo MODULO_PWM, do projeto acima discutido, foi gerado um símbolo para um novo projeto, denominado PWM_MOTOR, também disponibilizado abaixo para download. Este bloco é mostrado abaixo, juntamente com uma “LPM_CONSTANT” configurada para o valor 95, e um inversor para o sinal “HAB_SAIDA”, compatibilizando-o com o “HAB_SAIDAn” do bloco “MODULO_PWM”. O circuito será compilado para teste com uma barra de LEDs, ou o acionamento de um motor no conector CON1 do kit, e com barras de chaves nos conectores CON2 e CON3 para entrada dos sinais:

- HABILITA:Habilitação do PWM;

- INV_PWM: Inversão do sinal na saída de PWM,

- HAB_SAIDA: Habilitação da saída (“tri-state”) de PWM , e

- DT[7..0]: Razão cíclica para o PWM.

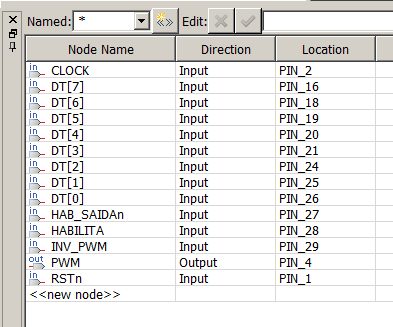

A atribuição de pinos projetada para o sistema é mostrada na figura seguinte:

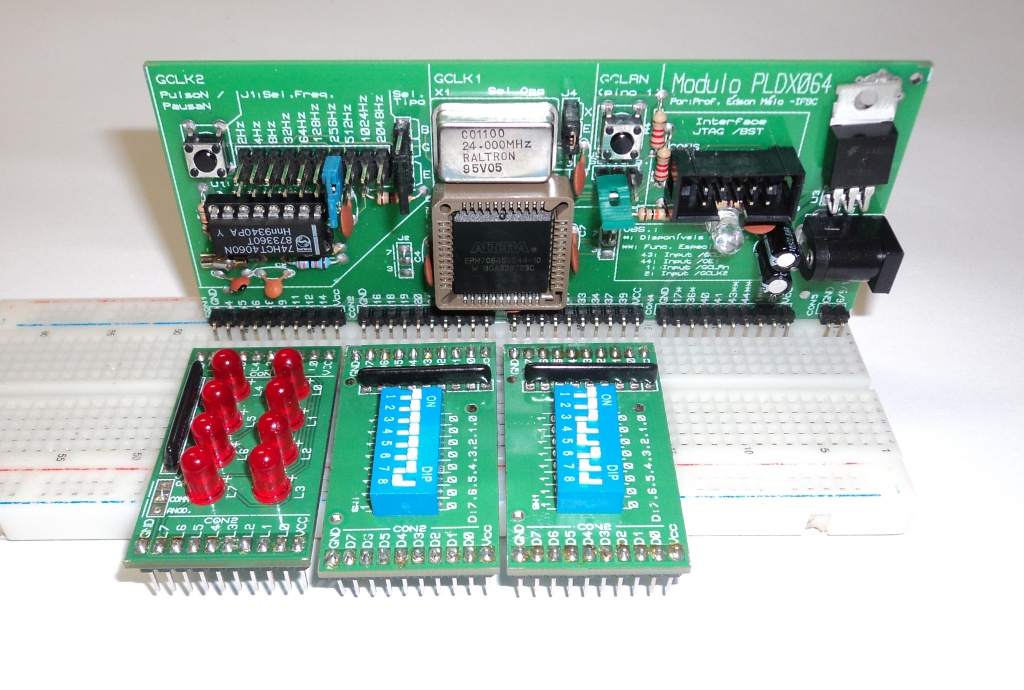

Após a compilação e a gravação, pode-se montar a estrutura do sistema, que deve ser como mostrado na figura abaixo.

Para teste do sistema, ajustam-se a razão cíclica desejada na barra de chaves do conector CON2. Os demais sinais são controlados na barra de chaves do conector CON3. O LED L7 da barra de LEDs terá a sua intensidade variada em função do sinal PWM gerado. Como vemos a seguir.

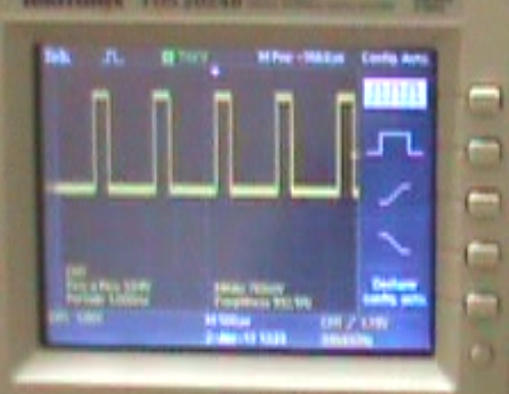

Na figura abaixo, mostramos uma imagem da onda, obtida com um osciloscópio. A frequência aproximada de 1KHz, e a razão cíclica de 25%, para o ajuste efetuado nas chaves, são verificadas.

Conclusão

Neste artigo foi demonstrado como gerar um sinal PWM através de diferentes maneiras tais como chavear a alimentação do circuito usando uma chave (botão), ou um transistor e também usando nosso kit PLD7064, porém existem outras maneiras de gerar um sinal PWM tais como microcontrolador ou até mesmo com circuitos usando CI 555.

Foi usado um LED para demonstração do efeito do sinal sobre a carga. O sinal irá influenciar no brilho do LED. Sabendo que existe uma infinidade de outras aplicações práticas tais como fontes chaveadas, controle de acionamento de motores, áudio, iluminação. Lembrando-se de que no circuito do LED a potência é baixa e o PLD fornece energia para o circuito sem a necessidade de uma fonte externa e um circuito de acionamento, entretanto outras aplicações com um consumo maior é necessário o uso de uma fonte externa, então o sinal PWM irá acionar um circuito para ligar e desligar essa fonte através de transistor ou mosfet por exemplo. Recomenda-se a leitura de exemplos de circuitos de controle acionados via PWM.

Videos e Artigos recomendados

Modulação por Largura de Pulso, áudio em inglês)

http://www.youtube.com/watch?v=Lf7JJAAZxEU

( exemplo usando motor, áudio em inglês)

http://www.youtube.com/watch?NR=1&feature=fvwp&v=mVx02s1fHIY

(áudio em inglês)

http://www.youtube.com/watch?v=4byHVqXD-UI

Artigo do Portal FPGA Para Todos.

Controle de LED RGB com PWM

Anexo

Projeto completo

Download Versão Demo do Proteus 8.

http://www.labcenter.com/download/prodemo_download.cfm#professional