Transmissão Serial - RS232

- Detalhes

- Categoria: Exemplos com CPLD

- Publicado em Quarta, 21 Setembro 2011 16:03

- Escrito por João Marcos de Aguiar

- Acessos: 4767

Transmissão Serial - RS232

O projeto a seguir tem por objetivo receber um byte de forma paralela e transmiti-lo através do modo serial, utilizando como base o protocolo RS232. O artigo recepção serial - RS232 é complementar a este projeto.

O artigo a seguir é um exemplo de projeto descrito em VHDL, o qual é simulado no software Modelsim-Altera®, através de um testbench utilizado como entrada de dados da simulação.

Serão utilizados nesse projeto:

- 1x kit CPLD_7064;

- 1x placa de botões;

- 1x placa de chaves;

- 1x kit uCduíno;

- 1x placa de LCD.

Descrição do Funcionamento

O protocolo RS232 inicia a transmissão com o envio de um start bit, em nível lógico baixo, para sincronizar a transmissão do dado, em seguida envia bit por bit, do LSB para o MSB, e por ultimo envia um stop bit, em nível lógico alto. O protocolo RS232 pode transmitir com diversas temporizações, neste caso se usará 9600 bits/s.

Figura 1: Forma de onda protocoloRS232

Para a transmissão do dado, será necessário registrar o dado, agrupá-lo com o start bit e o stop bit e então enviá-lo. Também é necessário esperar até que a transmissão tenha acabado para começar outra.

Figura 2: Ilustração esquemática do projeto

Descrição em VHDL

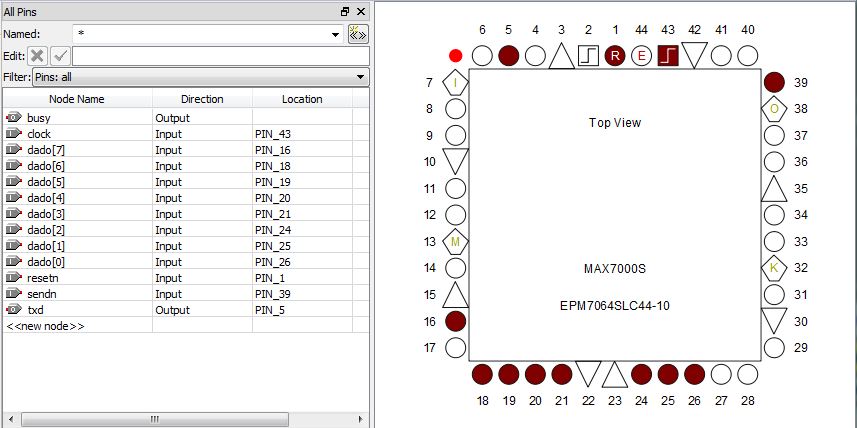

Neste projeto serão usadas 11 portas como entrada: Clock, Reset, Dado (8bits), bit de requisição de envio (sendn) e apenas uma saída, txd, bit de transmissão.

Dentro da architecture será necessário um sinal para armazenar o valor do dado e uma máquina de estados com os estados disponível e transmitindo.

Como será usado a taxa de 9600 bits/s, será necessário dividir o clock para a transmissão, pois o clock do kit é 24MHz. Para isso será necessário dividir o clock por 2500 no momento da transmissão. A variável contagem tem essa função. A variável conta_bits resgistrará quantos bits ja foram enviados.

O projeto pode ser dividido em duas partes: Reset, transmissão.

Quando Reset é pressionado, o programa volta às configurações iniciais.

Na transmissão, se está disponível, o programa verifica se foi solicitado o envio de dados, se sim ele muda o estado da maquina de estado, registra o dado a ser enviado concatenado com o start bit e o stop bit e zera a variável contagem.

Quando já está transmitindo, o programa precisa fazer a divisão do clock, portanto a cada pulso de clock é somado um na variável contagem. Quando contagem chega a 2500, o programa rotaciona os valores da variável que contém o dado para enviar o próximo bit, soma um a variável que conta a quantidade de bits enviado e atribui zero a variável contagem. Caso conta_bit seja 10, ou seja, já enviou 10 bits e a transmissão está encerrada, essa variável é zerada e o estado volta para disponível. O valor de txd (porta de envio de dados) que é enviado corresponde ao bit menos significativo da variável palavra_transmitir. Por ultimo, se atribui um sinal visual para o funcionamento, enquanto está transmitindo o circuito acenderá um LED.

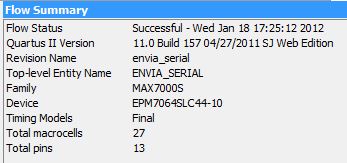

Figura 3: Resultado da analise e Sintese

Simulação

Para simular o funcionamento se usará o simulador Modelsim-Altera©. Na simulação basta mandar enviar alguns dados e verificar se os dados são enviados corretamente, lembrando que o envio ocorre do LSB para o MSB. A simulação do estado espera é feito no último bloco do teste, onde o valor da variável sendn continua em zero, de forma que a saída não deverá se alterar, mesmo com a alteração do bit de entrada.

Primeiramente, inicia-se a simulação com o botão de reset pressionado.

Em seguida, declara-se o bloco gerador de clock.

Para o teste do envio de dados, atribui-se valor de dados e envia um pulso no sendn para requisitar o envio do dado.

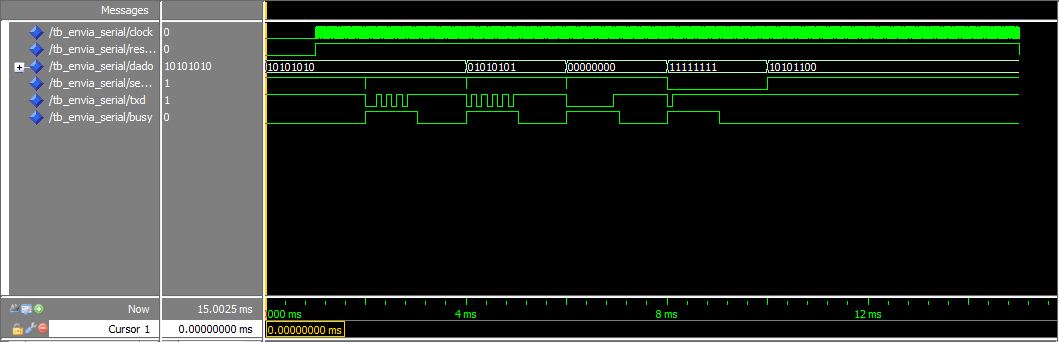

A simulação no Modelsim-Altera© apresentou as seguintes formas de ondas:

Figura 4: Simulação da transmissão de dados.

Estrutura Física

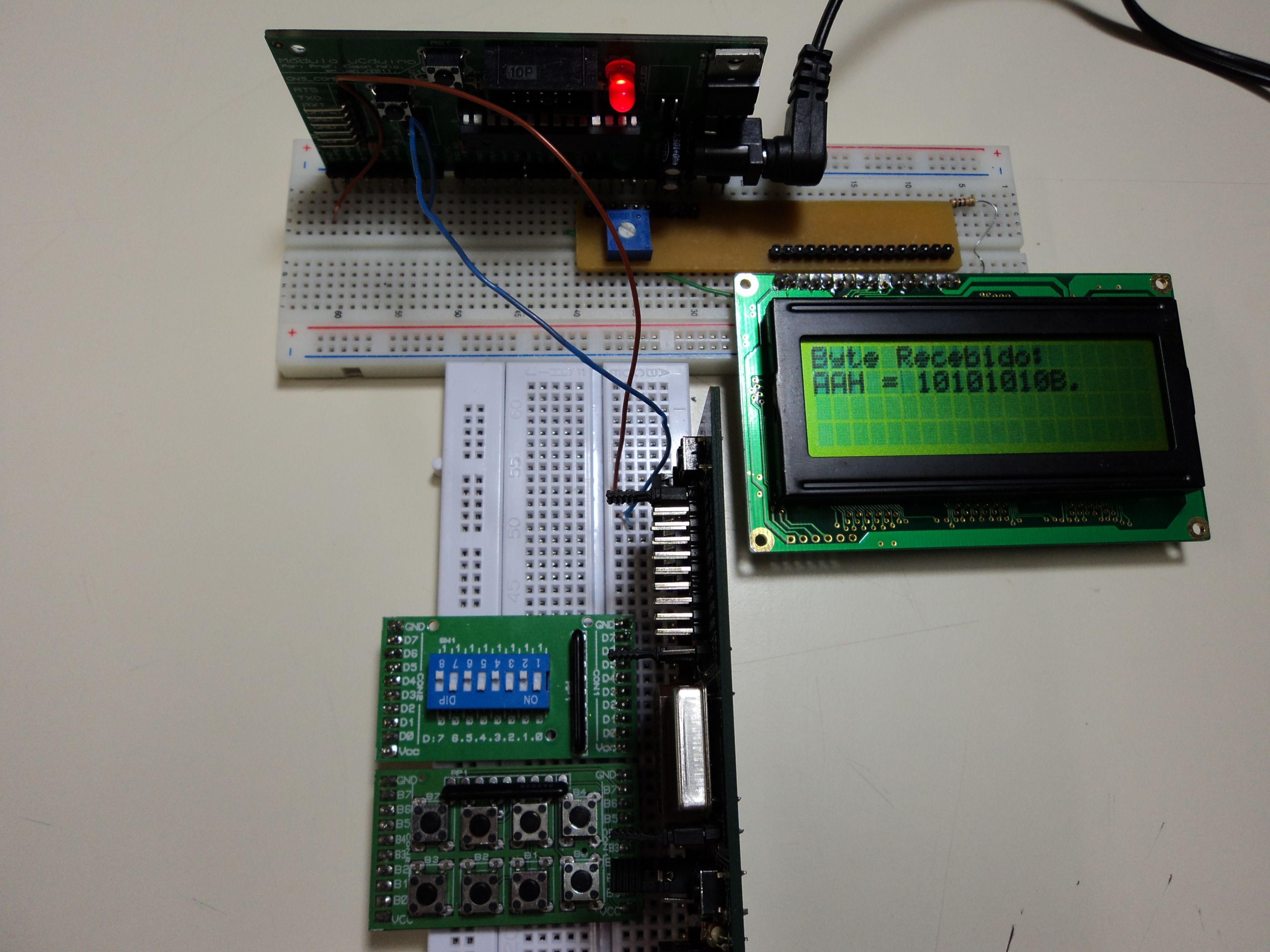

O funcionamento do projeto depende apenas do módulo CPLD_7064, mas para efetuar o teste, será utilizado a placa de chaves como dado de entrada, a placa de botões, usando apenas um botão para a requisição de envio, e um kit uCduíno para fazer a leitura do dado enviado e apresentá-lo em um display LCD, como mostra a figura 4. O componente usado para a gravação foi o EPM7064, da família MAX7000S.

Figura 5: Montagem do circuito de teste

Montagem e Roteamento

A montagem na protoboard segue os esquemas das figuras a seguir.

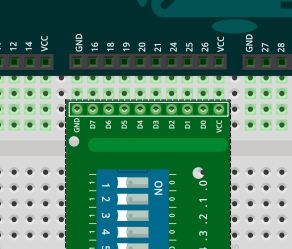

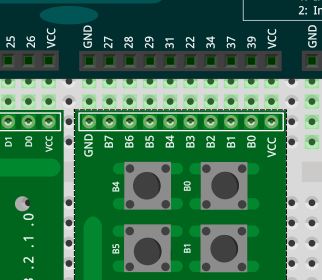

Figura 6: Conexão entre a placa de chaves e o módulo CPLD_7064

Figura 7: Conexão entre a placa de botões e o módulo CPLD_7064

Para a implementação do projeto, basta a utilização do módulo, devendo ser determinados os 8 pinos para o dado de entrada, um para o sinal de requisição de envio, um sinal de reset e um para o txd. Como a entrada será a placa de chaves, atribui-se os pinos da conexão CON2, de acordo com D0 até D7, sendo D0 o menos significativo. Quanto aos botões de requisição, optou-se pela tecla B0, correspondentes ao pino 39 do CPLD. Por ultimo, se atribuiu o pino 5 para txd. Para esse teste o sinal busy foi ignorado, pois o tempo em que ficaria ligado seria muito pequeno. Repare que o clock global 1 da placa (24MHz) corresponde ao pino 43 e o reset global no pino 1.

Figura 8: Atribuição de pinos para o projeto.

Gravação e Teste

A gravação pode ser feita seguindo o tutorial.

Para o teste, monta-se o módulo CPLD_7064 juntamente com o modulo das chaves, que funcionarão como dado de entrada, e a placa de botões para a requisição do envio do dado. Para isso, montou-se o circuito segundo a figura acima, em que o fio azul corresponde ao txd, o verde ao terra e o laranja a Vcc, dessa forma a placa do uCduíno está sendo alimentada pelo módulo CPLD_7064. O código utilizado no uCduíno está disponível juntamente com os arquivos de projeto. Durante o teste, foram feitos o envio de diversos dados e observado o dado transmitido no display LCD, como mostra o vídeo no início da página.